为什么我的处理器漏电?

问:为什么我的处理器功耗大于数据手册给出的值?

本文引用地址:http://www.amcfsurvey.com/article/201803/376686.htm答:在我的上一篇文章中,我谈到了一个功耗过小的器件——是的,的确有这种情况——带来麻烦的事情。但这种情况很罕见。我处理的更常见情况是客户抱怨器件功耗大于数据手册所宣称的值。

记得有一次,客户拿着处理器板走进我的办公室,说它的功耗太大,耗尽了电池电量。由于我们曾骄傲地宣称该处理器属于超低功耗器件,因此举证责任在我们这边。我准备按照惯例,一个一个地切断电路板上不同器件的电源,直至找到真正肇事者,这时我想起不久之前的一个类似案例,那个案例的“元凶”是一个独自挂在供电轨和地之间的LED,没有限流电阻与之为伍。LED最终失效是因为过流,还是纯粹因为它觉得无聊了,我不能完全肯定,不过这是题外话,我们暂且不谈。从经验出发,我做的第一件事是检查电路板上有无闪闪发光的LED。但遗憾的是,这次没有类似的、昭示问题的希望曙光。另外,我发现处理器是板上的唯一器件,没有其他器件可以让我归咎责任。客户接下来抛出的一条信息让我的心情更加低落:通过实验室测试,他发现功耗和电池寿命处于预期水平,但把系统部署到现场之后,电池电量快速耗尽。此类问题是最难解决的问题,因为这些问题非常难以再现“第一案发现场”。这就给数字世界的问题增加了模拟性的无法预测性和挑战,而数字世界通常只是可预测的、简单的1和0的世界。

在最简单意义上,处理器功耗主要有两方面:内核和I/O。当涉及到抑制内核功耗时,我会检查诸如以下的事情:PLL配置/时钟速度、内核供电轨、内核的运算量。有多种办法可以使内核功耗降低,例如:降低内核时钟速度,或执行某些指令迫使内核停止运行或进入睡眠/休眠状态。如果怀疑I/O吞噬了所有功耗,我会关注I/O电源、I/O开关频率及其驱动的负载。

我能探究的只有这两个方面。结果是,问题同内核方面没有任何关系,因此必然与I/O有关。这时,客户表示他使用该处理器纯粹是为了计算,I/O活动极少。事实上,器件上的大部分可用I/O接口都没有得到使用。

“等等!有些I/O您没有使用。您的意思是这些I/O引脚未使用。您是如何连接它们的?”

“理所当然,我没有把它们连接到任何地方!”

“原来如此!”

这是一个令人狂喜的时刻,我终于找到了问题所在。虽然没有沿路尖叫,但我着实花了一会工夫才按捺住兴奋之情,然后坐下来向他解释。

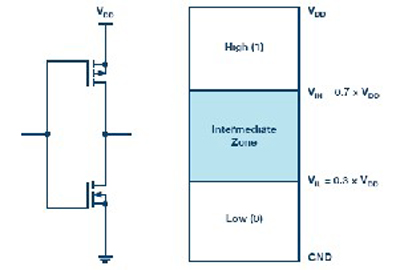

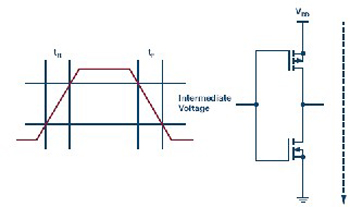

典型CMOS数字输入类似下图:

当以推荐的高(1)或低(0)电平驱动该输入时,PMOS和NMOS FET一次导通一个,绝不会同时导通。输入驱动电压有一个不确定区,称为“阈值区域”,其中PMOS和NMOS可能同时部分导通,从而在供电轨和地之间产生一个泄漏路径。当输入浮空并遇到杂散噪声时,可能会发生这种情况。这既解释了客户电路板上功耗很高的事实,又解释了高功耗为什么是随机发生的。

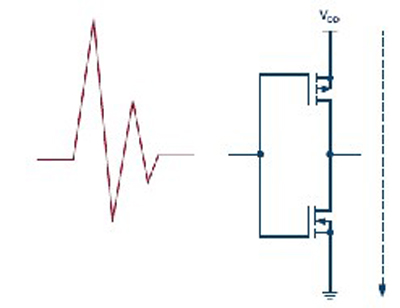

图2.PMOS和NMOS均部分导通,在电源和地之间产生一个泄漏路径

某些情况下,这可能引起闩锁之类的状况,即器件持续汲取过大电流,最终烧毁。可以说,这个问题较容易发现和解决,因为眼前的器件正在冒烟,证据确凿。我的客户报告的问题则更难对付,因为当您在实验室的凉爽环境下进行测试时,它没什么问题,但送到现场时,就会引起很大麻烦。

现在我们知道了问题的根源,显而易见的解决办法是将所有未使用输入驱动到有效逻辑电平(高或低)。然而,有一些细微事项需要注意。我们再看几个CMOS输入处理不当引起麻烦的情形。我们需要扩大范围,不仅考虑彻底断开/浮空的输入,而且要考虑似乎连接到适当逻辑电平的输入。

如果只是通过电阻将引脚连接到供电轨或地,应注意所用上拉或下拉电阻的大小。它与引脚的拉/灌电流一起,可能使引脚的实际电压偏移到非期望电平。换言之,您需要确保上拉或下拉电阻足够强。

如果选择以有源方式驱动引脚,务必确保驱动强度对所用的CMOS负载足够好。若非如此,电路周围的噪声可能强到足以超过驱动信号,迫使引脚进入非预期的状态。

我们来研究几种情形:

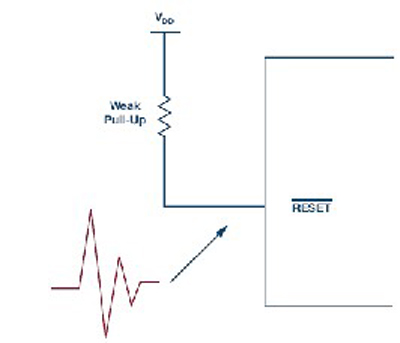

1.在实验室正常工作的处理器,在现场可能莫名重启,因为噪声耦合到没有足够强上拉电阻的RESET(复位)线中。

图3.噪声耦合到带弱上拉电阻的RESET)引脚中,可能引起处理器重启

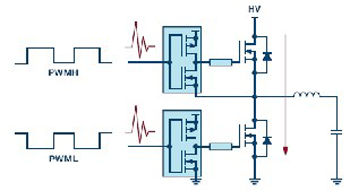

2.想象CMOS输入属于一个栅极驱动器的情况,该栅极驱动器控制一个高功率MOSFET/IGBT,后者在应当断开的时候意外导通!简直糟糕透了。

图4.噪声过驱一个弱驱动的CMOS输入栅极驱动器,引起高压总线短路

另一种相关但不那么明显的问题情形是当驱动信号的上升/下降非常慢时。这种情况下,输入可能会在中间电平停留一定的时间,进而引起各种问题。

图5.CMOS输入的上升/下降很慢,导致过渡期间暂时短路

我们已经在一般意义上讨论了CMOS输入可能发生的一些问题,值得注意的是,就设计而言,有些器件比其他器件更擅长处理这些问题。例如,采用施密特触发器输入的器件能够更好地处理具有高噪声或慢边沿的信号。

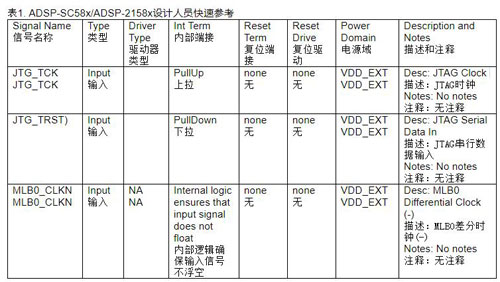

我们的一些最新处理器也注意到这种问题,并在设计中采取了特殊预防措施,或发布了明确的指南,以确保运行顺利。例如,ADSP-SC58x/ADSP-2158x数据手册清楚说明了有些管脚具有内部端接电阻或其他逻辑电路以确保这些管脚不会浮空。

最后,正如大家常说的,正确完成所有收尾工作很重要,尤其是CMOS数字输入。

评论