放大器电路设计方案精选

模拟设计是电路设计中至关重要的一环。本文汇集2014年以来,EDN China杂志发表的一些放大器、数字模拟转换器等模拟设计实例,希望会对您有所帮助。

本文引用地址:http://www.amcfsurvey.com/article/201710/369296.htm差分输入/输出低功耗仪表放大器

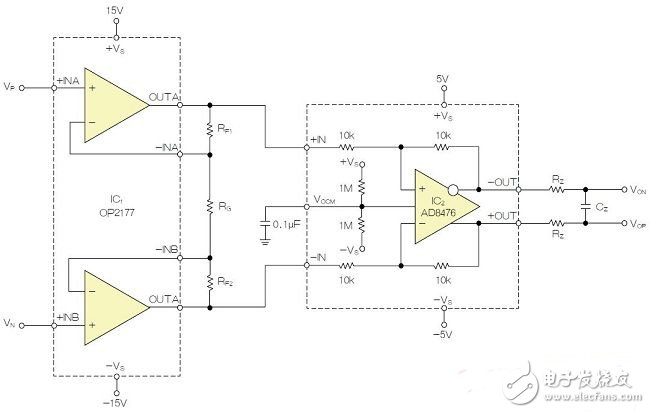

目前所有市售的三运放仪表放大器仅提供了单端输出,而差分输出的仪表放大器可使许多应用从中受益。全差分仪表放大器具有其他单端输出放大器所没有的优势,它具有很强的共模噪声源抗干扰性,可减少二次谐波失真并提高信噪比,还可提供一种与现代差分输入ADC连接的简单方式。图1显示了低功耗全差分仪表放大器电路的实现方式。

低功耗全差分仪表放大器

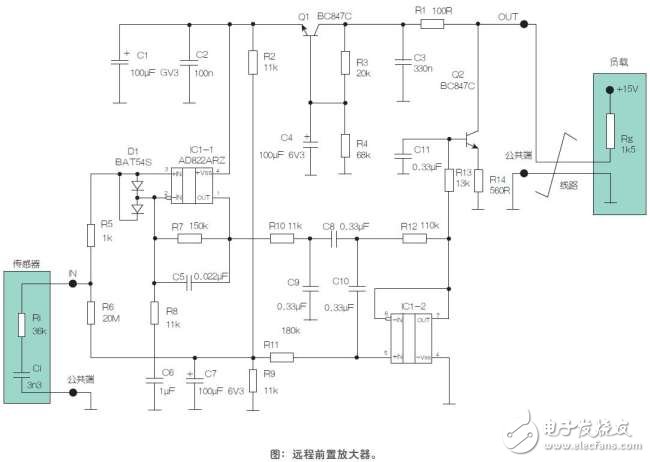

双线远程传感器前置放大器

本设计实例实现了一种远程传感器前置放大器(如用于压电式传感器),其可通过单个导线对或同轴电缆传输信号和电能。AD822ARZ是一个真正的单电源供电运算放大器,其具有轨到轨输出、极低的输入电流和低频噪声,适合与高阻抗信号源同时工作。AD822具有5V的单电源供电能力,这使其成为本设计实例的佳选。[ 点击查看全文 ]

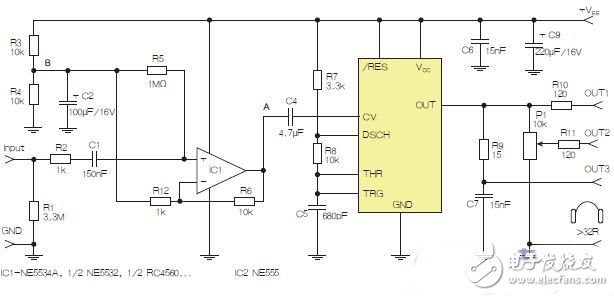

基于555定时器的D类耳机驱动器可作为理想的实用放大器

广受欢迎的555定时器可用作乐器或其他应用的PWM/D类放大器。其可在4.5V~16V的电源电压范围内工作,并可输出200mA的驱动电流。音频信号被传送至555定时器的CV( 控制电压)引脚。本设计实例为耳机和音频线路提供两个简单、便宜的驱动器。这两个驱动器针对电吉他和小提琴设计,但也可适用于更多其他应用。对于这样的简单应用而言,噪声和总谐波失真(THD)并不是重点考虑因素,因此并未对这两个数值进行测量。

含运算放大器和NE555定时器的耳机和音频线路驱动器。也可以使用CMOS版本(如LMC555),但输出电流较低。其优点为工作频率较高。

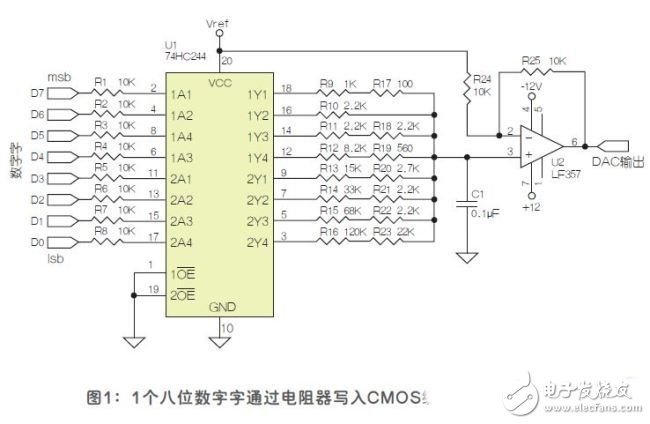

使用八进制CMOS缓冲器的二象限乘法DAC

本设计实例使用一个八进制CMOS缓冲器的大工作电压范围,呈现一个由缓冲器/线驱动器IC74HC244组成的简单的八位二象限乘法数字模拟转换器(DAC)。如图1所示,一个八位数字字通过电阻器R1~R8写入CMOS缓冲器U1的八个输入中。U1的各个输出通过由电阻器R9~R23组成的 1:2:4:8.。.128加权电阻网络产生。DAC参考电压Vref馈送给U1VCC,因此,U1的输出电压跟踪Vref的变化。电阻器R1~R8必须要使U1的输出电压免受数字输入的电压水平的影响。[ 点击查看全文 ]

面向精准放大器应用的匹配电阻器网络

某些理想的运算放大器配置会假定反馈电阻器呈现完美的匹配。而事实上,电阻器的非理想性会对各种电路参数产生影响,如共模抑制比(CMRR)、谐波失真和稳定性。

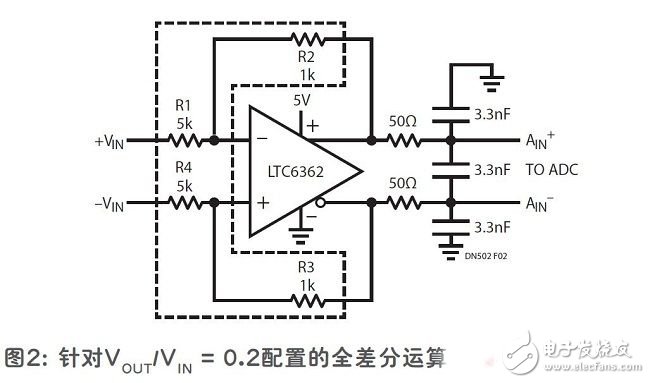

本设计要点将LT5400与厚膜、0402、1%容差表面贴装型电阻器进行了对比,研究了采用这些电阻器在一个LTC6362运算放大器周围提供反馈(如图2所示)时的CMRR、谐波失真和稳定性。

评论