如何避免PCB设计限制D类放大器性能?

介绍

本文引用地址:http://www.amcfsurvey.com/article/201710/367324.htm如果没有遵循一些基本的布局指南,PCB设计将会限制D类放大器的性能或降低其可靠性。下面描述了D类放大器一些好的PC板布局实践经验。采用带有两个BTL输出的STA517B(每通道175瓦)数字功率放大器作为范例,但对所有的D类放大器而言,其基本概念是一致的。

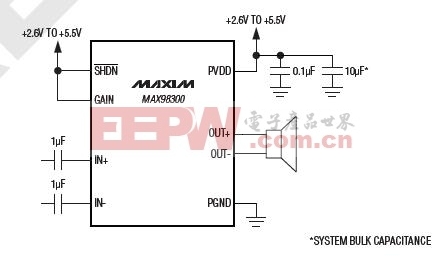

图1:立体声BTL D类功率放大器原理图

地平面

良好的地平面是优质D类放大器布局的关键。如果可能应将电路板的底层作为一个专有的地平面,完整的地平面可以提供最佳性能和最可靠的设计。如果你不得不在电路板的底层布信号线或电源走线,须尽可能的短。如果必要,为了使底层走线短距离,应将走线引回到电路板的顶层,从而避免在底层长距离走线。

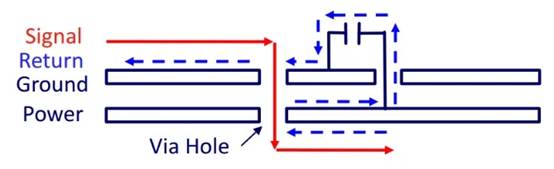

利用过孔将电路板的顶层器件与电路板底层的地平面连接。但是,过孔仍会堵塞电流回流到地平面,因此须灵活的使用这些过孔。

直接在放大器之下的区域须敷铜。如果放大器在其封装的底部有一个裸露的焊盘或插件,那么IC必须焊接到放大器下放的地,如此可以作为放大器的扇热区。在这种情况下,地必须从IC正下方向两边引出,这样可以确保其裸露。放大器下面的地须打上许多过孔,通过过孔向电路板的底层扇热,因此它还可以作为一个扇热区域。

放大器的正下方是不建议走信号线的。须打几个过孔和地平面相连以确保所有器件彼此之间的地参考点有一个直接和低阻抗的路径。这对输出滤波器是尤为重要的。所有的滤波地必须有一个直接路径回流到放大器正下方的地平面。

电源旁路电容

为确保稳定性及抑制噪声和串扰,对电源加旁路电容是非常重要的。放大器的输出级吸收了大量的电流,且开关动作迅速。当输出开关动作时,旁路电容和放大器电源输入引脚之间的寄生电感会产生很大的毛刺,因此寄生电感必须保持尽可能的小。为了能在放大器功率级减小杂散电感和旁路电容之间谐振的影响,须在每个电源输入管脚需使用一个100nF的电容与1uF的电容并联。

100nF的电容必须和IC尽可能的靠近(通常不超过2毫米)。而且,如图1所示,旁路电容必须和IC在同一层,以便减小总路径长(和杂散电感)。1uF的电容须依次放置,和100nF电容紧靠在一起。

图2:利用电路板的底层为100nF电容进行地连接,如此将明显的增加总走线长且对电路板性能会产生不良影响。

还需采用大体积储能电容在放大器的电源输入进行去耦。大体积储能电容的容值依赖于放大器所要求的电流量。大体积储能电容须和放大器以及电源管脚星形连接,且必须和放大器尽可能的靠近(理想情况是小于30毫米)。

图3:100nF旁路电容须紧靠IC放置。

图4:1uF电容需放置在100nF电容之后,通过过孔将1uF电容和电路板底层的地平面连接。

评论