详析数字I/O和逻辑分析仪常用术语

本文介绍了数字I/O和逻辑分析仪的常用术语和定义。

本文引用地址:http://www.amcfsurvey.com/article/201710/366604.htm1.抖动

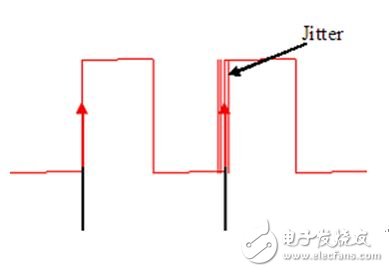

抖动是指与事件理想时序的偏差,并通常基于参考信号的过零点进行测量。 抖动通常来自于串扰、同步开关输出和其它定期发生的干扰信号。 由于抖动会随时间变化,抖动的测量和量化既可以是秒级范围内视觉估计,也可以是基于统计的测量,比如基于标准偏差随时间变化的统计测量。

图1.数字信号抖动示例

2.偏移

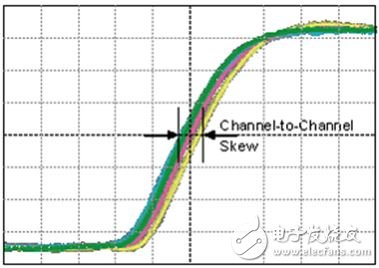

对于定时(动态)生成,通道间偏移定义为两个数据通道对应边沿之间的时间差。 例如,如果两个数据通道均设置为在特定采样时从低电平转换为高电平,两个通道上升沿之间的时间差就是两个通道之间的通道间偏移。

对于动态采集,通道间偏移定义为每个数据通道采样时间之间的差。 每次采集采样点时,每个数据通道进行采样的时间是不相同的,但是它们之间的时间差非常小,通常会落在某个特定的时间窗口内。 这个时间窗口就称为通道间偏移。

下图显示了一组信号的通道间偏移。

图2.数字信号偏移示例

指定的通道间偏移一般是指某个设备上所有数据信道之间的偏移。

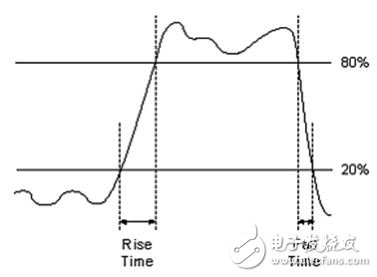

3.上升时间和下降时间

上升时间(trise) 是指信号在高低电平之间从高电平的20%上升到80%所经历的时间。 下降时间 (tfall)是指信号在高低电平之间从高电平的80%下降到20%所经历的时间。

图3.数字信号上升时间和下降时间图

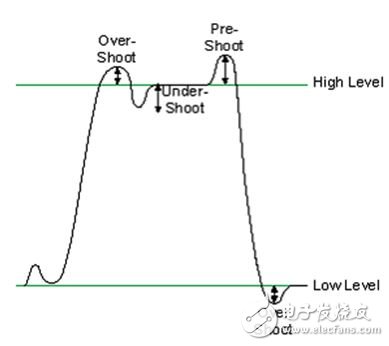

4.过冲和下冲

前冲和过冲主要指脉冲上升或者下降沿前(前冲)或后(过冲)的脉冲瞬时电平峰值失真。 图4显示了信号前冲和过冲的一个例子。

注意:过冲、前冲和下冲均是不正常现象。

图4.数字信号过冲、前冲和下冲图

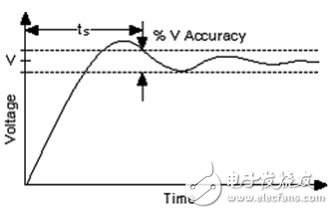

5.稳定时间

稳定时间(tS)是指放大器、继电器或其它电路达到稳定运行所需的时间。 对于信号采集而言,满幅阶跃的稳定时间是指信号达到一定的精度并保持在这个精度范围内所经历的时间。

图5.数字信号的稳定时间图

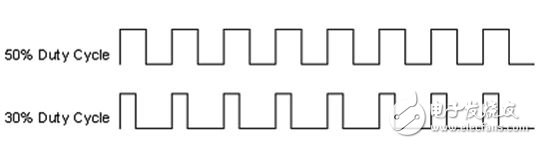

6.占空比

对于时钟信号,占空比是指波形处在逻辑高电平的时间与波形周期之间的比值。 下图显示了两个具有不同占空比波形之间的差异。 请注意,占空比为30%的波形处于逻辑高电平的时间少于占空比为50%的波形。

图6. 数字信号占空比图

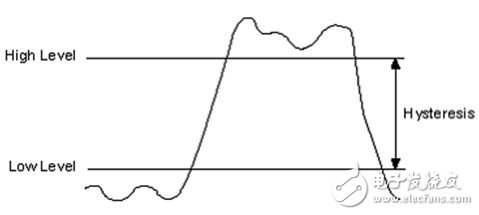

7.迟滞

迟滞是指检测到信号从逻辑高电平转变为逻辑低电平和从逻辑低电平转变为逻辑高电平时的电压电平之差值。 请参阅图7的迟滞图解。

图7.数字信号的迟滞图

所有数字逻辑器件的数字输入均存在一定程度的迟滞。 特定设备的滞环幅值可以通过以下公式计算得到:

迟滞 ≈ VIH - VIL

在输入端数字信号的上升沿,设备在VIH时检测到信号从逻辑低电平转变为逻辑高电平。 相反地,当设备输入端电压低于VIL时设备检测到信号的电平从逻辑高变为逻辑低。

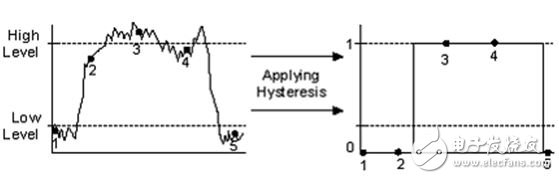

迟滞是数字设备一个非常有用的属性,因为它可在一定程度上抑制数字系统的高频噪声。 这种噪声通常是由逻辑电平转换的高边沿速率反射引起的,如果仅使用一个电压阈值来确定逻辑状态的变化,该噪声可能会导致数字设备进行错误的电平转换检测。 这一现象可通过图8清晰看出。

图8.噪声可能对迟滞造成的影响

在该图中,第一个采样点为一个逻辑低电平。 第二采样点也是一个逻辑低电平,因为信号电平尚未冲过高电平阈值。 第三和第四个采样点是逻辑高电平,第五个采样点是逻辑低电平。

对于具有固定电压阈值的设备,系统的噪声抗扰度(NIM)和迟滞是由系统的组件决定。 例如,部分NI数字I/O设备可允许您控制系统的NIM和迟滞。 系统NIM和迟滞可使系统具有一定的噪声抗扰度,但对于特定的逻辑设备,通常需要在这两者之间做出权衡——迟滞越大,NIM越小;反之亦然。 如果要正确设置电压阈值,您必须仔细检查系统的信号质量,以确定您是需要在高低电平时获得更高的抗噪性能(更高的NIM)还是需要在逻辑电平转换时获得更高的抗噪性能(更高的滞环)。

评论