同步降压转换器的布局注意事项

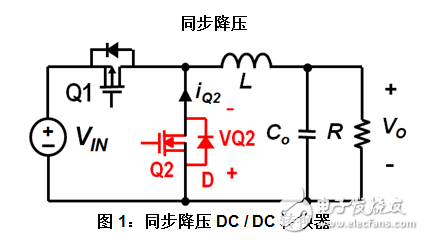

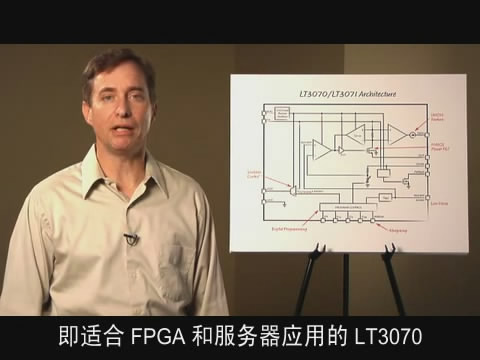

降压DC/DC转换器(见图1)是一种非常受欢迎的开关DC / DC稳压器拓扑,广泛应用于许多电气和电子,从云基础设施到个人电子产品,再到工厂和楼宇自动化。它们占据了当今所有非隔离开关稳压器拓扑75%以上的份额。

本文引用地址:http://www.amcfsurvey.com/article/201710/365874.htm降压转换器的布局与模拟和设计一样重要,但如果缺乏良好的布局实践可能会拖延开发时间,甚至造成操作和可靠性问题。

布局考虑的因素包括旁路电容器、反馈补偿网络组件、功率组件、寄生组件、接地回路和连接。

旁路电容器

对于旁路电容,最小化引线电感很重要,可通过减小旁路回路面积、缩短高di / dt(电流转换速率)路径上的长度、尽可能使用接地层(如可能)、在电容器两端引入电流路径、避免多种布局等方案来实现。此外,并联不同的电容器类型以降低电容频带两端的阻抗很重要,因为它可以把2MHz至20MHz频率范围(典型的电容器值为0.1μF至0.01μF)的阻抗降低。牵引电容,使其更靠近集成电路(IC)引脚,还能向布局设计者展示关键节点和面积,如图2所示。

反馈补偿网络

将补偿网络置于靠近IC误差放大器的地方。放置电阻,使它们直接连接到误差放大器(FB引脚)的反相输入,如图3所示。

电源组件

确保正确连接电源组件,因为电流路径中有高di / dt(电流转换速率),如图4所示。路径中的任何电感将导致开关节点振铃,这可能超过功率FET的绝对最大额定值,并且还会在系统中产生谐波和不必要的噪声。目标是通过使用双面印刷电路板(PCB)的装配来最小化回路面积,其中在PCB的一侧上具有MOSFET(金属氧化物半导体场效应晶体管),而在另一侧上具有电容器。确保正确地放置和布设组件。正确的设计无需缓冲电路来减少开关节点振铃。

寄生组件

注意寄生元件,因为它们可能引入并增加电源中的阻抗,这会导致稳定性和操作问题。注意接线电感,特别是低阻抗电路和滤波器、电源开关和定时电路。使用接地层和宽走线以最小化电感。在电路板电容方面,注意高阻抗或噪声敏感电路,并注意电路板平面/层和组件焊盘之间的耦合。电感器之间,特别是环形电感器,也可能发生磁耦合。这种情况下,请考虑其他安装方向。磁耦合也可能发生在环路之间,因此,应最小化环路面积并使用接地平面。

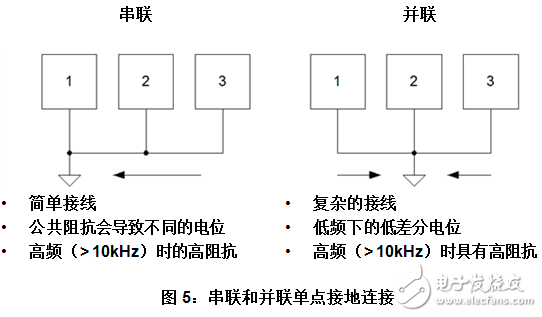

接地回路和连接

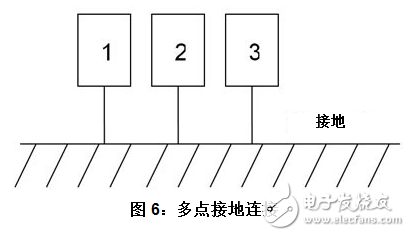

更好的方法是使用多点接地。如图6所示,多点接地允许电路之间具有低阻抗,以最小化电位差,并且还减少了电路走线电感。目的是在单个电路中包含高频电流,并将其保持在接地平面之外。

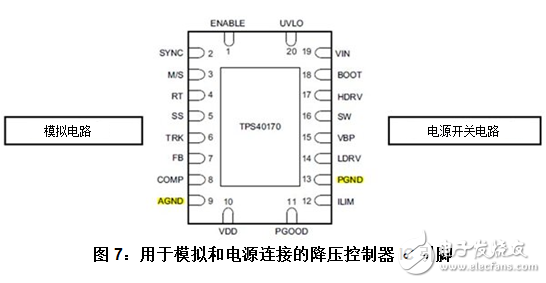

许多降压转换器控制IC可识别噪声和安静的电路区域,并且IC引脚如此排列,使得IC引脚周围的布局和元件布置更加容易。有些甚至为电源和模拟接地提供单独的引脚,如图7所示的TPS40170 60V同步降压脉冲宽度调制(PWM)控制器引脚。

因此,围绕IC引脚布局进行布局规划,并使用本文中提到的布局实践可帮助您从一开始就获得正确的降压转换器设计,并避免以后出现任何麻烦。查看TI的降压转换器和降压控制器选择表,了解各种降压DC / DC解决方案。

评论