数字隔离器:解决汽车xEV应用中的设计难题

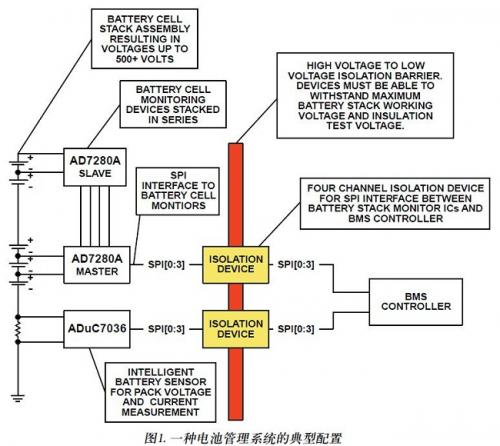

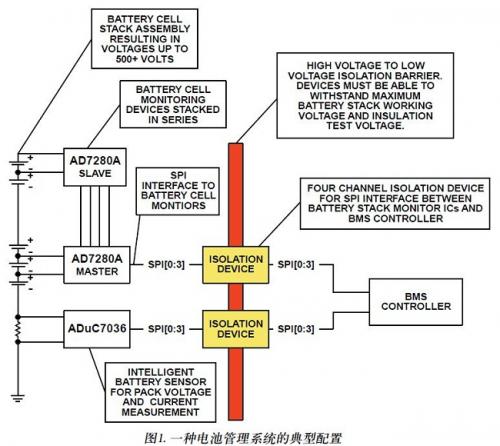

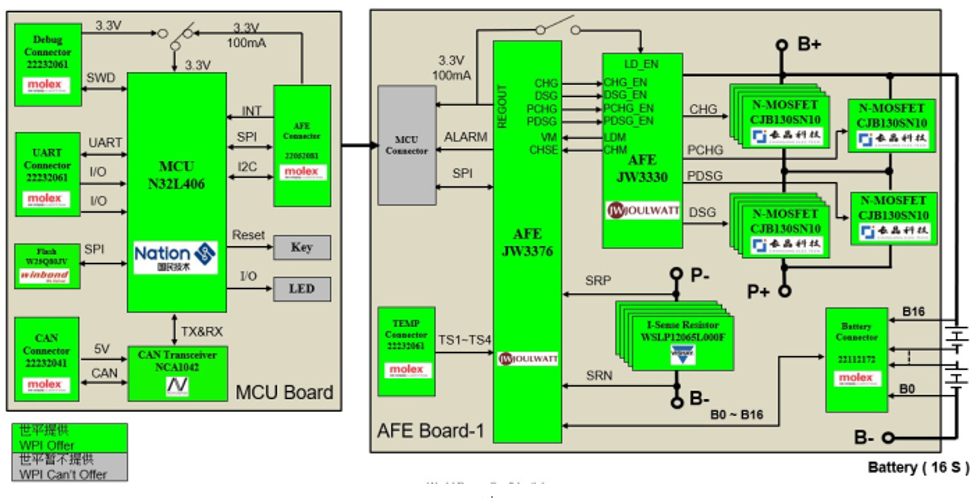

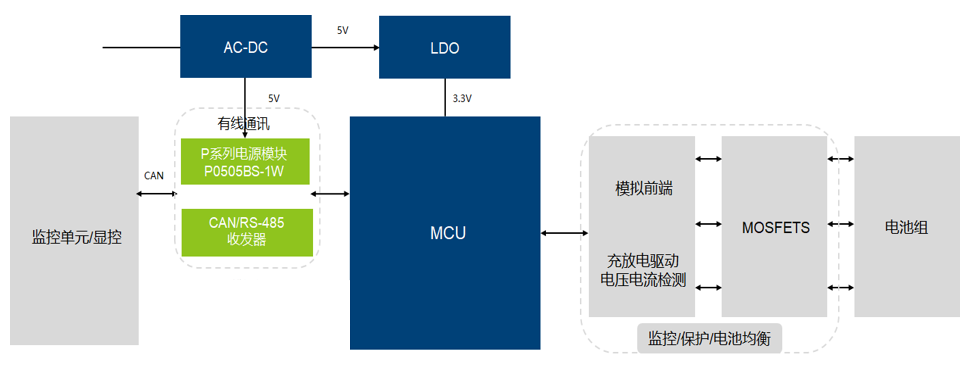

在为汽车xEV应用开发解决方案时,设计师会遇到的一个难题是如何在高压电池域与低压电池域电子元件之间传递数字数据。这一难题出现在多种应用之中,比如电池电压监测、电池电流测量、高压接触器监测、电机控制等。一种典型的电池管理系统(BMS)应用如图1所示,其中高亮显示的几个区域需要数字信号隔离,接下来我们将以其为基础,探讨各种设计考虑因素。

本文引用地址:http://www.amcfsurvey.com/article/201706/350583.htm

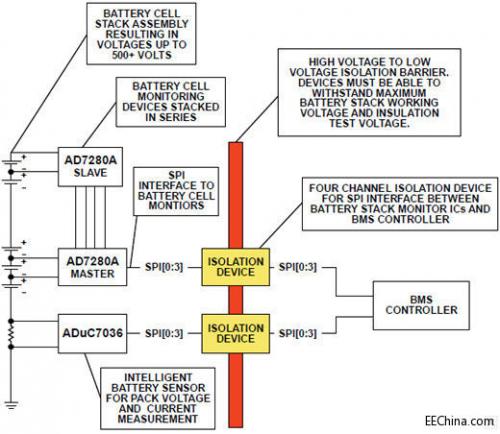

在BMS应用中,设计师需要开发一种解决方案,将来自各种集成电路的高速数字信号跨过隔离栅进行传输。对于本设计示例,这种高速数字信号即是串行外设接口(SPI)连接,用于BMS控制器与电池监测电子元件之间的通信。隔离栅必须保护工作于典型的12 V汽车电压域的BMS控制器电子元件,使其免受以高压(最高可达500V)电池域为基准的电子元件的影响,同时还须具有卓越的耐受力,能承受车辆电力传动系统产生的高压电池瞬变。隔离栅和隔离器件非常重要,因为它们不但保护着车辆的电子元件,同时还保护着车辆乘客,使其免受高压电池产生的电击风险的影响。

对于隔离栅要求,设计师可以参阅各种行业标准,以确定印刷电路板设计的适用指南。对于数字隔离器件的选择,设计师则会遇到诸多难题,必须考虑几个关键性能参数,比如:器件功耗、PCB空间限制、数据速率/数据一致性(通道间匹配)、以及适当的隔离和工作电压(在汽车整个生命周期)。本文将探讨器件功耗和PCB板空间限制问题。

在上述两个难题的基础上,可以探讨如何确定正确的元件解决方案。对于数字隔离,目前市场上有多种技术可用,而在选择元件时可以考虑两种技术:基于光耦合器的隔离和基于数字技术的隔离。光耦合器通过LED产生光的方式进行工作,光通过一个透明隔离栅传导至一个光检测器,而数字隔离器则是采用高速CMOS工艺设计,集成空芯微变压器。

需要考虑的第一个设计难题是器件的功耗,结果将为设计师带来两个挑战。静态吸电流是xEV电子设计关注的重点之一,因为车辆在关断状态下的功耗会导致高压电池组最后一次已知充电状态出现偏差。另外,将电动汽车中全部电子模块的功耗相加时,电子电路的工作功耗也是一个令人头疼的问题。两种情况下,目标是将功耗降至最低。为了解决静态功耗问题,我们可以设计BMS,禁用非必要电路的源电压供应,结果可以消除设计师的这一顾虑。然而,对于隔离器件所需工作电流,数字隔离器与光耦合器之间存在较大的差量。假设为电池监测应用使用一个1 MHz的SPI接口,则对于SPI通信总线所需要的四个数字隔离通道而言,像ADI ADuM1401一样的数字隔离器将消耗2.4 mA的低压域工作电流和1.4 mA的高压域工作电流。该值适用于以下工作条件:典型汽车5 V的工作电压范围以及汽车扩展 ?40°C至+125°C的工作温度范围。与之相当的基于光耦合器的解决方案,每个隔离通道至少需要4 mA的电流,而设计师还须考虑5 V电压范围和工作温度的变化。考虑这些变化会使每个隔离通道的吸电流提升至10 mA,结果使同一SPI通信总线的低压域工作电流达到30 mA,高压域工作电流则达10 mA。相对于传统光耦合器解决方案,ADuM1401一类的数字隔离器在工作功耗方面具有显著优势。

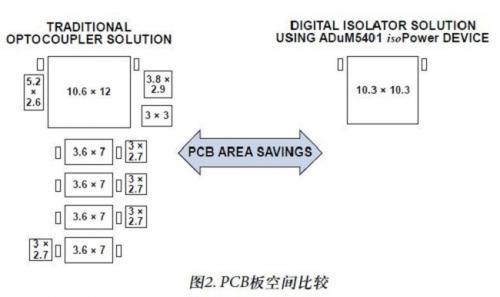

需要解决的第二个难题是BMS电子设计工程师面临的机械设计限制。在BMS开发中,PCB面积是一种珍贵的资产,设计师必须构建出能适用于超紧凑区域的解决方案。高压至低压接口的间距要求(一般称为爬电距离和间隙)由各种电气标准定义,元件必须符合这些标准针对给定应用规定的最低要求。对数字和光耦合器两种隔离解决方案进行了比较,以确定哪种方案可以为PCB板节省大量空间。

对于数字隔离解决方案,我们将考察ADuM1401。ADuM1401采用16引脚SOIC_W封装,其标准JEDEC封装尺寸为10.3mmx10.3mm,元件总面积为106mm2。与之相当的光耦合器解决方案要求四个5引脚SOIC封装器件,其标准JEDEC封装尺寸为7.0mmx3.6 mm,单元件面积为25.2 mm2。需要在PCB板上放置四个元件,而器件之间一般需要1.2mm的间距。将光耦合器解决方案所需PCB板总面积相加,设计师必须留出134.5 mm2的空间。显然,使用数字隔离器解决方案,设计师已经可以节省大约28 mm2的面积。

在限定隔离器件面积之后,设计师接下来要考虑整个解决方案所需要的支持元件。数字隔离器(如ADuM1401) 需要使用两个外部旁路电容。假设采用0603封装电容, 则占用面积为2.5 mm2。对于典型的光耦合器解决方案, 设计师必须增加四个电阻(5.1 mm2)、四个电容(5.1 mm2) 和四个前驱电路(33 mm2),因为多数微控制器无法处理其GPIO引脚的10mA功耗要求。至此,设计师可以看到,在需要考虑PCB板面积时,数字隔离器具有明显优势。与PCB空间相关的另一设计考虑是隔离器件的高压端的驱动问题。对于BMS应用,需要在电池监测器件上实现功耗的均衡化,以防止电池组出现内在的不平衡。对于光耦合器解决方案,需要一个单独的DC-DC转换器,用于提供隔离工作电压以驱动高压端接口,结果将进一步增加PCB板的面积要求。在数字隔离器件中,设计师可以选择ADuM5401数字隔离器,其中含有四个SPI接口隔离通道,同时还集成了用于驱动高压端接口的DC-DC转换器功能。其封装尺寸与ADuM1401数字隔离器相同,因此,不会增加PCB板的面积要求。

与传统的光耦合器模式相比,数字隔离器解决方案为设计师提供了一种节省空间的隔离器件实现方案,如图2所示。

总之,xEV电子元件设计工程师面对的数字隔离难题可以借助数种不同的隔离拓扑结构而予以解决。通过运用数字隔离器,设计师可以为其应用实现功耗和PCB板面积的双节省。

相关阅读:

数字隔离器大观,原理,应用案例,设计技巧,选型要素

评论