理解FPGA中的压稳态

本白皮书介绍FPGA 中的压稳态,为什么会出现这一现象,它是怎样导致设计失败的。介绍怎样计算压稳态MTBF,重点是对结果造成影响的各种器件和设计参数。

引言

当信号在不相关或者异步时钟域之间传送时,会出现压稳态,它是导致包括FPGA 在内的数字器件系统失败的一种现象。本白皮书介绍FPGA 中的压稳态,解释为什么会出现这一现象,讨论它是怎样导致设计失败的。

通过计算压稳态导致的平均故障间隔时间(MTBF),设计人员知道是否应采取措施来降低这类失败的概率。

本白皮书解释怎样利用各种设计和器件参数来计算MTBF, FPGA 供应商和设计人员怎样提高MTBF。可以通过设计方法和优化措施来降低出现压稳态失败的概率,从而提高系统可靠性。

什么是压稳态?

FPGA 等数字器件中的所有寄存器都有确定的信号时序要求,使每一个寄存器能够正确的采集输入数据,产生输出信号。为保证能够可靠的工作,寄存器输入必须在时钟沿之前稳定一段时间( 寄存器建立时间,即tSU),在时钟沿之后也要保持稳定一段时间( 寄存器保持时间,即tH)。一定的时钟至输出延时 (tCO) 之后,寄存器输出有效。如果信号转换不能满足寄存器的tSU 或者tH 要求,寄存器输出就有可能进入压稳态。在压稳态中,寄存器输出在高电平和低电平状态之间徘徊一段时间,这意味着,输出延时超出设定的tCO 之后才能转换到确定的高电平或者低电平状态。

在同步系统中,输入信号必须满足寄存器时序要求,因此,不会出现压稳态。信号在不相关或者异步时钟域电路之间传输时,一般会出现压稳态问题。在这种情况下,由于信号可能在相对于目的时钟的任意时间到达,因此,设计人员不能保证信号能够满足tSU 和tH 要求。然而,并不是所有不能满足寄存器tSU 或者tH的信号转换都导致压稳态输出。寄存器是否会进入压稳态以及返回稳定状态所需要的时间与器件制造工艺以及实际工作条件有关。在大部分情况下,寄存器会很快返回稳定状态。

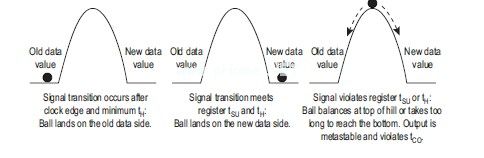

可以把寄存器在时钟边沿采样数据信号形象的看成是球从山上滚落下来,如图1 所示。山的两边代表稳定状态——信号转换之后,信号的老数据和新数据,山顶代表压稳态。如果球从山顶滚落,它会处于不确定状态,实际中,它稍偏向一侧,然后,落到山下。从山顶开始,越到山脚,球到达底部稳定状态的速度越快。

图 1. 利用球从山上落下描述压稳态

如果数据信号在时钟沿之后以最小的 tH 转换,这就类似球从山的“老数据值”一侧落下,输出信号保持在该时钟转换的最初值不变。当寄存器数据输入在时钟沿之前以最小 tSU 转换,保持时间大于最小 tH,这就类似球从山的“新数据值”一侧落下,输出信号很快达到稳定的新状态,满足确定的tCO 时间要求。但是,当寄存器数据输入不能满足tSU 或者 tH, 时,这就类似于球从山顶落下。如果球落在山顶附近,那么,它会花很长时间才能落到山脚,增加了时钟转换到稳定输出的延时,超出了要求的tCO。

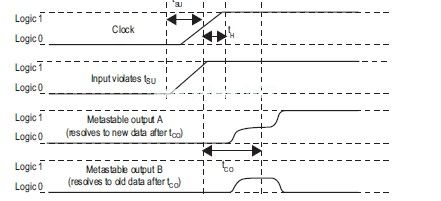

图2 描述了压稳态信号。时钟信号转换时,输入信号从低电平状态转换到高电平状态,不能满足寄存器的tSU 要求。数据输出信号从低电平状态开始,进入压稳态,在高电平和低电平状态之间徘徊。信号输出A 转换到输入数据的新逻辑1 状态,输出B 返回到数据输入最初的逻辑0 状态。在这两种情况下,输出转换到确定的1 或者0 状态的时间被延迟了,超出了寄存器要求的tCO。

图 2. 压稳态输出信号实例

压稳态什么时候会导致设计失败?

如果数据输出信号在寄存器下次采集数据之前,转换到有效状态,那么,压稳态信号不会对系统工作有不利影响。但是,如果压稳态信号不能在它到达下一设计寄存器之前转换到低电平或者高电平状态,那就会导致系统失败。继续山和球的形象解释,当球到达山脚( 稳定逻辑状态0 或者1) 的时间超出分配的时间后,即,寄存器tCO 加上寄存器通路所有时序余量的时间,就会出现失败。当压稳态信号没有在分配的时间内稳定下来时,如果目的逻辑观察到不一致的逻辑状态,即,不同的目的寄存器采集到不同的压稳态信号值,出现逻辑失败。

同步寄存器

当信号在不相关或者异步时钟域电路之间传送时,在使用该信号之前,需要将信号同步到新的时钟域。新钟域中第一个寄存器起到了同步寄存器的作用。

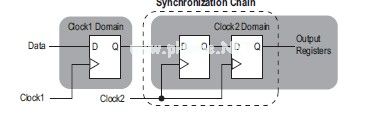

为消除异步信号传送时压稳态导致的失败,电路设计人员通常在目的时钟域中使用多个串联寄存器( 同步寄存器链或者同步器),将信号重新同步到新时钟域上。采用这些寄存器,在设计中的其他部分使用压稳态信号之前,该信号能够有更多的时间转换到确定状态。同步寄存器至寄存器通路上的时序余量是压稳态信号稳定所需要的时间,被称为压稳态稳定时间。

同步寄存器链或者同步器是满足以下要求的寄存器序列:

■ 链上的寄存器都由相同的或者相位相关的时钟进行同步

■ 链上的第一个寄存器由不相关的时钟域进行驱动,即异步驱动。

■ 每个寄存器只扇出连接一个寄存器,链上的最后一个寄存器除外。

同步寄存器链的长度是满足以上要求的同步时钟域中的寄存器数量。图3 是长度为2 的同步链的例子,假设输出信号被送入多个目的寄存器。

图 3. 同步寄存器链实例

注意,异步输入信号,或者在不相关时钟域之间传输的信号,会在相对于采集寄存器时钟沿的任意点进行转换。因此,设计人员无法预测数据转换前的信号转换顺序或者目的时钟边沿数量。例如,如果在时钟域之间传送异步总线信号,并进行同步,数据信号会在不同的时钟沿进行转换。结果,会接收到不正确的总线数据。

设计人员必须适应这种电路工作方式,例如,双时钟 FIFO (DCFIFO) 逻辑存储信号或者握手逻辑等。FIFO逻辑使用同步器在两个时钟域之间传送控制信号,然后,数据被写入双端口存储器,或者读出。Altera 为这一操作提供DCFIFO 宏功能,它包括各种级别的延时,为控制信号提供亚稳态保护。如果异步信号被用作两个时钟域之间的部分握手逻辑,控制信号会指出数据什么时候才能在时钟域之间进行传输。在这种情况下,采用同步寄存器以确保亚稳态不会影响控制信号的接收,在任何亚稳态条件下,数据都有足够的建立时间,在使用数据之前达到稳定。在设计比较好的系统中,每一信号在被使用之前都能达到稳定状态,设计可以正常工作。

计算亚稳态MTBF

亚稳态平均故障间隔时间MTBF 大致估算了亚稳态导致出现两次设计失败之间的平均时间。较大的MTBF( 例如亚稳态失败间隔数百甚至数千年) 表明非常可靠的设计。所需要的MTBF 取决于系统应用。例如,急救医疗设备需要的MTBF 要比消费类视频显示设备长得多。增大亚稳态MTBF 能够减小信号传输导致设备出现亚稳态问题的概率。

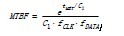

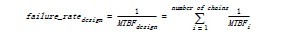

可以使用设计信息以及器件特征参数来计算设计中某些信号传输或者所有信息传输的亚稳态MTBF。采用下面的公式和参数来计算同步器链的MTBF:

在fCLK 和fDATA 参数取决于设计规范: fCLK 是接收异步信号时钟域的时钟频率, fDATA 是异步输入数据信号的触发频率。较快的时钟频率以及触发数据能够降低( 或者劣化) MTBF。

tMET 参数是亚稳态信号达到确切状态的亚稳态建立时间,即,超出寄存器tCO 的时序余量。同步链的 tMET 是链上每一寄存器输出时序余量之和。

设计中每一同步器链的MTBF 确定了总的设计MTBF。同步器的失效率是1/MTBF,将每一同步器链的失败概率相加得到整个设计的失败概率,如下所示:

设计人员使用Altera® FPGA 时,不需要手动完成这些计算,这是因为Altera Quartus® II 软件将亚稳态参数集成到了工具中。

确定亚稳态常数

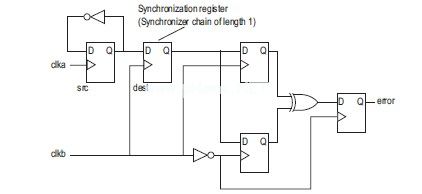

FPGA供应商可以通过FPGA的亚稳态特性来确定MTBF方程中的常数。确定特性的难点在于典型FPGA设计的MTBF 一般在几年以上,因此,使用真实设计,在实际工作条件下测量亚稳态事件之间的时间间隔是不可行的。为确定器件亚稳态常数, Altera 使用了测试电路,设计的这一电路具有较短的可测量MTBF,如图4 所示。

在这一设计中, clka 和clkb 是两路不相关的时钟信号。同步器输入数据在每一时钟周期进行触发( 较大的fDATA)。同步器长度为1,这是因为一个同步寄存器连接了两个目的寄存器。目的寄存器在一个时钟周期后以及一个半时钟周期后采集同步器输出。如果信号在下一时钟沿到达之前进入亚稳态,电路探测到采样信号出现了不同,输出一个错误信号。这一电路能够探测到半时钟周期内出现的大部分亚稳态事件。

在器件中很多地方复制了这一电路,以减小本地差异的影响,对每一例化模块进行连续测试,以消除耦合噪声。Altera 对每一测试结构测量一分钟,记录错误数。以不同的时钟频率进行测试,在对数坐标上画出MTBF 与tMET 的关系。常数C2 对应于试验结果趋势线的斜率,以常数C1 线性标出曲线。

提高亚稳态MTBF

由于MTBF 方程中的指数因子, tMET/C2 项对MTBF 计算的影响最大。因此,可以通过优化器件常数C2,改进体系结构来提高亚稳态性能,或者优化设计,增大同步寄存器的tMET。

改进FPGA 体系结构MTBF 方程中的亚稳态时间常数C2 取决于器件制造工艺技术相关的各种因素,包括晶体管速率和供电电压等。采用较快的工艺技术和速度更快的晶体管,亚稳态信号能够很快达到稳定。FPGA 从180-nm 工艺尺寸发展到90 nm,晶体管在提高速度的同时也增大了亚稳态MTBF。因此,亚稳态并不是FPGA 设计人员主要考虑的问题。

然而,随着工艺尺寸的减小,供电电压随之降低,电路阈值电压并没有成比例下降。当寄存器进入亚稳态时,其电压大约是供电电压的一半。供电电压降低后,亚稳态电压电平接近电路中的阈值电压。当这些电压比较接近时,电路增益降低了,寄存器需要较长的时间才能脱离亚稳态。FPGA 进入65-nm 以及更小的工艺尺寸之后,供电电压降到0.9V 以下,相对于晶体管速度的提高,应重点考虑阈值电压的影响。因此,除非供应商设计FPGA 电路来提高亚稳态可靠性,否则,亚稳态MTBF 会越来越差。

altera 利用FPGA 体系结构亚稳态分析功能来优化电路,提高亚稳态MTBF。Altera 40-nm Stratix® IV FPGA体系结构以及新器件在设计上进行改进,降低了MTBF 常数C2 ,从而提高了亚稳态的可靠性。

设计优化

MTBF 方程中的指数因子意味着增大设计相关tMET 值能够指数增大同步器MTBF。例如,如果某一器件的常数C2,设置工作条件为50 ps,那么, tMET 只需要增大200 ps,就能够实现指数200/50,提高MTBF e4 倍,即50 多倍,而增大400 ps,提高MTBF e8 倍,即3000 倍。

另一方面,最差MTBF 链对设计MTBF 的影响最大。例如,考虑具有10 个同步链的两个不同设计。一个设计的10 个链有相同的10,000 年MTBF,另一设计的9 个链有一百万年的MTBF,但是一个链的MTBF为100 年。设计失败概率是每一链的失败概率之和,失败概率为1/MTBF。第一个设计的亚稳态失败概率为10 个链× 1/10,000 年 = 0.001,因此,设计MTBF是1000 年。第二个设计的失败概率为9 个链 × 1/1,000,000 +1/100 = 0.01009,设计MTBF 为99 年,略小于最差链的MTBF。

换言之,设计较差的同步链决定了设计的亚稳态总MTBF。由于这一效应,对所有异步信号和时钟域传输进行亚稳态分析非常重要。设计人员或者工具供应商提高最差MTBF 同步链的tMET ,会对设计MTBF 有很大的影响。

为提高亚稳态MTBF,设计人员可以在同步寄存器链上增加额外的寄存器级,以提高tMET 。增加的每一寄存器至寄存器连接时序余量被加到tMET 值中。设计人员一般使用两个寄存器来同步信号,而Altera 建议使用三个寄存器作为标准,以实现更好的亚稳态保护。然而,增加一个寄存器会在同步逻辑中加入额外的延时级,因此,设计人员必须综合考虑这是否可行。

如果设计使用Altera FIFO 宏功能,跨时钟域使用单独的读写时钟,那么,设计人员可以增强亚稳态保护(和延时),实现更好的MTBF。Altera Quartus II MegaWizard™ 插件管理器提供增强亚稳态保护选项,包括三个甚至更多的同步级 。

Quartus II 软件还提供业界最好的亚稳态分析和优化功能,以增大同步寄存器链的tMET。确定同步器后,软件将同步寄存器靠近放置,以增加同步链的输出时序余量,然后报告亚稳态MTBF。

结论

信号在不相关或者异步时钟域电路之间传输时,会出现压稳态问题。亚稳态失败平均时间间隔与器件工艺技术、设计规范和同步逻辑的时序余量有关。FPGA 设计人员可以通过增大tMET ,采用增加同步寄存器时序余量等设计方法来提高系统可靠性,增大亚稳态MTBF。Altera 确定了其 FPGA 的MTBF 参数,改进器件技术,从而增大了亚稳态MTBF。使用Altera FPGA 的设计人员可以利用Quartus II 软件功能来报告设计的亚稳态MTBF,优化设计布局以增大MTBF。

致谢

■ Jennifer Stephenson,应用工程师,软件应用工程技术组成员, Altera 公司。

■ Doris Chen,软件和系统工程高级软件工程师, Altera 公司。

■ Ryan Fung,软件和系统工程技术组资深成员, Altera 公司。

■ Jeffrey Chromczak,软件和系统工程资深软件工程师, Altera 公司。

(发布者:chiying)

评论