系统级语言SystemVerilog和SystemC的融合

随着项目复杂程度的提高,最新的系统语言的聚合可以促进生产能力的激增,并为处在电子设计自动化(EDA)行业中的设计企业带来益处。SystemVerilog和SystemC这两种语言在设计流程中的共存,可以带来显著的实际利益和经济效果。

本文引用地址:http://www.amcfsurvey.com/article/201706/349320.htmSystemVerilog和SystemC不久前依然被视为相互排斥的两种环境,而现在可以相互协作,并为实现设计和验证方法提供平滑流畅的系统。

在真实设计流程中的经验清楚地表明,这两种语言非但不是相互对立,而且还是一种互补的关系。将两种语言在同一种环境下使用,会带来确实的利益并明显缩短项目周期。

SystemC和SystemVerilog在不同的设计领域中,分别有各自的特点。两种标准的结合,将从系统规范、门电路布局直至设计验证,为设计人员提供一种可供选择的综合语言环境。这种结合可以看作是工具和语言相统一的转变潮流中的重要部分,这种统一是为了支持最终用户的需求,而不仅仅是为了方便工具供应商。

SystemVerilog应运而生

SystemVerilog在一种语言中结合了现代的设计和验证环境,因此消除了当今在芯片设计过程中的大量瓶颈。通过建立在Verilog的基础上,这种语言可在现有的基于Verilog的流程中采用更多的不同功能,从而使设计者在认知过程中少走弯路。

通过结合Verilog与C语言大量的最佳特性,SystemVerilog易于使用、为人们所熟悉,并提供实现简明设计和自动化测试平台的特征。而且,由于SystemVerilog语言是Verilog的扩展集,因此在现有环境下使用相当方便。

SystemVerilog 3.0为硬件设计团队的简明设计提供了强大的基础,使模型很快生成并易于纠错。最新版SystemVerilog 3.1还为创建现代化的测试平台增加了关键的验证功能。

操控简明的设计与验证平台

SystemVerilog包含所有Verilog源语言,包括Verilog IEEE 1364委员会2001年增加的新功能。一流的生成功能、经过简化的端口处理、动态变量及各种其他功能使Verilog使用起来更加直截了当。

SystemVerilog 3.0含有列举类型和构件等丰富的basic C编程功能。SystemVerilog 3.1(将于2003年年中推出)新版本将增加面向特定目标的性能及其他大量重要功能,从而使Verilog用户在编程方面具有全面的灵活性,这对于验证和系统建模处理是至关重要的。

SystemVerilog3.0主要改善设计过程中的RTL编码工作,最新版中含有的各种专用功能,可以更加简明地编写综合化的RTL代码,减少工时和故障风险。此外,经强化后,新的接口构件提供了生成新的编码字段的能力,允许更深程度的提取和与架构环境的链接,同时大大提高了设计的透明度,在这一层面上还引入了判断功能,这样,设计人员可以在代码中加入规范元素,进一步提高板块级的验证自动化。

统一验证提高工作效率

如果SystemVerilog3.0旨在提高设计效率,那么3.1版则侧重于提高验证效率。SystemVerilog为测试平台开发提供单独、一致的语法和语义。这种语言中包含丰富的判断功能,这是制定验证场合详细规范所必需的。新版本具备功能运行环境和自动化的测试生成器,也提供强大的交易层测试的编程特性,适用于系统和设计实现的验证。

SystemVerilog通过一种独立、简单的聚合性语言可以满足所有的验证需求。

SystemVerilog与SystemC

SystemC由于其开放式状态,已在设计界得到广泛认可,从而拥有大量功能强大、可互操作的基于SystemC的工具和技术。 SystemC主要优点是能够以开放式C++扩展语言的形式,利用标准软件语言并添加结构性和系统性功能,处理硬件和软件的协同设计和集成。SystemC正被愈来愈多地用于生成片上系统(SoC)设计的虚拟原型。这些以SystemC或SystemVerilog编码的虚拟原型,可应用在交易层,允许信号细节为达到有效性能而被替换。

尽管含有大量允许使用交易层设计分析的系统特性,但SystemVerilog主要还是用于实现设计和验证。对于从事RTL级设计和验证的工程人员来说,这种语言可以通过多种功能显著改善设计流程。

然而,对于当今的方法原理来说,只满足纯粹RTL设计的要求是不够的。嵌入式处理器的使用正在迅速增长,与之伴随发展的是解决专门纵向领域问题的完整工程平台。SystemVerilog含有大量功能,可满足基于平台设计的要求,特别是在这一环境下对可重用知识产权(IP)的使用。采用接口实现标准通信机制建模、检查协议相符的系统判断、由C/C++到HDL一对一映射编程性能,这些都使嵌入式环境易于进行数据和控制转移。

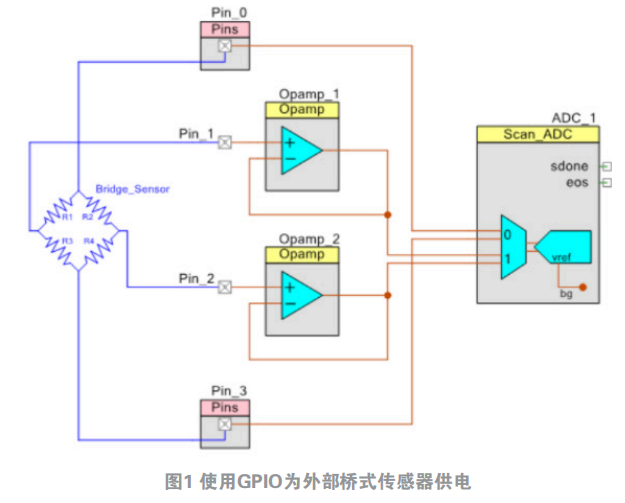

嵌入式系统开发需要将模型提供给硬件设计人员和软件专业人员。SystemC的设计考虑到了这一问题,在系统层提供了用于平台建模的有效机制。C/C++设计模型是必须为硬件和软件工程人员提供的,而且基于硬件的功能对于有效的、高效率的硬件建模是必要的。

处理这种对分环境最有效的方法是允许这些语言共存。平台的基本构件是可以用C或HDL派生语言、信号或交易层建模的IP。这个IP可以采取由架构层开始的设计构件的形式,然后进一步细化到实施。验证组件也可以采取IP形式,用于在系统层生成协议流或其他标准I/O。这些IP组件包含系统验证要求,并且利用相应的总线功能模型可供其他验证流程重复使用。

SystemVerilog配置了专用接口。通过这些接口,总线功能接口可以以一种对系统或实施工程师透明的方式进行编码。由于这些接口含有对通讯有效性、C/C++到HDL的转变以及总线功能编码的判断功能,从而为从架构到实施建立平滑的途径提供了完整的机制。这样,两种环境下的用户可以用自己习惯的方法处理模型,不必再进入另一个区域。

注重使用模型而不是偏重设计语言,这表明SystemVerilog 和SystemC两种语言都在现代电子方法中占有自己的位置。

Synopsys公司认识到,同时提供对SystemC和SystemVerilog的支持对最终用户是有益的。Synopsys是支持SystemC的发起者,并一直通过公开OpenVera测试平台语言、共用的API和OpenVera Assertion(OVA)格式致力于推进语言的标准化进程。为了使SystemVerilog 3.1能够做出上述贡献,SystemVerilog包含了能够简化RTL设计所需的全部功能。

用语言的功能平衡用户的需求

现已证明,C语言设计不仅生产效率高,而且也是对Verilog流程的补充。SystemVerilog/SystemC的整合,使软件团队可以在与高效的硬件设计和验证过程开展合作的时候,用自有的编程语言进行工作,使整个方法途径在适宜的生产水平下进行。

工具和IP供应商正在为System Verilog提供支持。IP提供商已认识到统一化所带来的益处,特别是在验证领域,语言的统一使他们不必考虑当前支持多种语言的需求。

评论