FPGA系统设计的仿真验证之: FPGA设计仿真验证的原理和方法

7.1FPGA设计仿真验证的原理和方法

7.1.1FPGA设计仿真验证

严格来讲,FPGA设计验证包括功能与时序仿真和电路验证。仿真是指使用设计软件包对已实现的设计进行完整测试,模拟实际物理环境下的工作情况。

本文引用地址:http://www.amcfsurvey.com/article/201706/348822.htm功能仿真是指仅对逻辑功能进行测试模拟,以了解其实现的功能是否满足原设计的要求。仿真过程没有加入时序信息,不涉及具体器件的硬件特性,如延时特性等,因此也叫前仿真。它是对HDL硬件设计语言的功能实现能力进行仿真,以确保HDL语言描述能够满足设计者的最初意图。

时序仿真则是在HDL可以满足设计者功能要求的基础上,在布局布线后,提取有关的器件延迟、连线延时等时序参数,并在此基础上进行的仿真,也称为后仿真,它是接近真实器件运行的仿真。

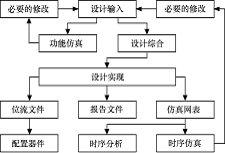

如图7.1所示是FPGA设计仿真验证的基本方法。

图7.1FPGA设计仿真验证基本方法

7.1.2FPGA设计仿真的切入点

在FPGA的设计中,完整的设计流程往往会涉及多个EDA工具,比如设计输入工具、综合工具、布局布线工具、仿真工具等。如何将这些EDA工具进行适当的结合,在符合各个工具接口情况下发挥各个工具的特长,是每一个FPGA设计工程师都要面临的问题。

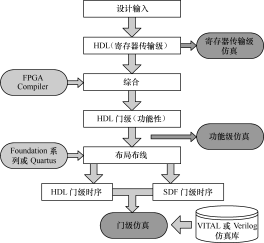

如图7.2所示是利用仿真工具ModelSim与综合工具FPGACompilerII及布线工具FoundationSeries或Quartus相配合实现FPGA设计的流程图。

图7.2FPGA设计仿真切入点

在设计输入阶段,由于Modelsim仅支持VHDL或VerilogHDL,所以在选用多种设计输入工具时,可以使用文本编辑器完成HDL语言的输入。当然也可以利用相应的工具以图形方式完成输入,但必须能够导出对应的VHDL或VerilogHDL格式。

近年来出现的图形化HDL设计工具,可以接收逻辑结构图、状态转换图、数据流图、控制流程图及真值表等输入方式,并通过配置的翻译器将这些图形格式转化为HDL文件,如MentorGraphics公司的Renoir,Xilinx公司的Foundation系列都带有将状态转换图翻译成HDL文本的设计工具。

从图7.2可以看出,在FPGA设计过程中,有3处可以使用Modelsim进行仿真。

(1)寄存器传输级(RTL)仿真。

此级仿真是对设计的语法和基本功能进行验证(不含时序信息)。在RTL仿真阶段,应该建立一个测试台。此测试台可以在整个FPGA流程中进行仿真验证(RTL级、功能级、时序门级)。测试台不但提供测试激励与接收响应信息,而且可以测试HDL仿真流程中的关键功能(如运算部件输出值的正确性等)。测试台的产生可以直接使用文本编程得到,也可以使用图形化工具输入,再由软件翻译为HDL格式,例如使用HDLBencher软件利用其良好的波形输入界面输入测试激励,再由其自动转化为HDL格式而得到。

(2)针对特定的FPGA专有技术的仿真。

此级仿真是在综合后、实现前而进行的功能仿真。功能仿真一般验证综合后是否可以得到设计者所需要的正确功能,而且功能仿真的结果往往与RTL级仿真结果相同。

(3)门级仿真。

此级仿真是针对门级时序进行的仿真,门级仿真体现出由于布局布线而产生的实际延时。在这个阶段,仿真的结果和设计者选择的FPGA型号有着直接的关系。由于不同的FPGA的内部结果有所差异,因此同一个设计在不同FPGA型号上得到的门级仿真结果也是不同的。

评论