基于ARM与FPGA控制的LTC2207在宽带频率特性测试仪数据采集中的应用

引言

数据采集技术是一种流行且实用的电子技术。它广泛应用于信号检测、信号处理、仪器仪表等领域。近年来,随着数字化技术的不断发展,数据采集技术也呈现出速度更高、通道更多、数据量更大的发展趋势。

本设计中数据采集系统的核心器件是凌力尔特公司的A/D转换芯片LTC2207.本文研究了在ARM核S3C2440芯片和FPGA的控制下对直流数据和正弦信号的采集应用,并进行了相关的仿真验证。

1 LTC2207芯片介绍

1.1 LTC2207的功能特性

LTC2207是16位A/D转换器,它的采样速率为105Msps.LTC2207是针对输入频率为700 MHz的高频、宽动态范围信号进行数字化处理而设计的。它可以利用PGA前端(输入范围为1.5Vp-p或2.25Vp-p)对该ADC的输入范围进行优化。

LTC2207非常适合于要求苛刻的通信应用。它的AC性能包括78.2 dB噪声层和100 dB无杂散动态范围(SFDR);250 MHz时SFDR>83 dB(输入范围为1.5Vp-p时);80fSRMS的超低抖动实现了高输入频率的欠采样和卓越的噪声性能;最大DC规格包括整个温度范围内的±4LSB INL、±1LSB DNL(无漏失码)。

LTC2207具有单一的3.3 V供电电源,单一的电源允许CMOS输出摆幅为0.5~3.6 V.它同时具有700MHz全功率带宽S/H(采样及保持),可选的内部抖动和数据输出(Randomizer)随机函数发生器,功耗为900 mW.LTC2207可利用正弦波时钟、PECL、LVDS、TTL或CMOS输入对ENC+和ENC-输入进行差分或单端驱动。可任选的时钟占空比稳定器在全速和多种时钟占空比条件下实现了高性能。

LTC2207的引脚说明略一一编者注。

1.2 LTC2207的时序说明

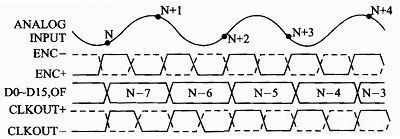

LTC2207时序图如图1所示。LTC2207是带有前端PGA的CMOS多步转换器。模拟输入是差分信号以提高共模噪声抑制,最大限度地利用输入范围。此外,差分输入信号可以降低取样保持电路的谐波。编码输入也比共模抑制输入具有更强的抗干扰能力。

图1 LTC2207时序图

LTC2207的采集取决于ENC+/ENC-输入引脚的状态,由图1可知LTC2207在ENC+引脚的上升沿时(ENC-引脚的下降沿时)采样模拟输入信号。它有5个流水线模数转换阶段,经过7个周期后,一个模拟采样输入就会转换为一个数字值。数字输出上/下溢出则由OF引脚上的逻辑高电平表示。

此A/D转换器有一个延迟的编码输入作为数字输出,提供了CLKOUT+和CLKOUT-两信号;需要使用正弦时钟编码信号CLKOUT+/CLKOUT-将数据同步转换到数字系统。数据在CLKOUT+的上升沿或CLKOUT-的下降沿锁存,在CLKOUT+下降沿和CLKOUT-上升沿时更新。

2 硬件电路设计

信号采集部分主要完成对模拟信号的调理和A/D转换芯片的采集。A/D转换芯片的输入信号是差分的,而被采集的信号是单端的,这就需要把单端信号转换成差分信号。输入的信号经过MAX4201缓冲后,由差分驱动器AD8131转换成差分信号,驱动A/D转换芯片LTC2207.

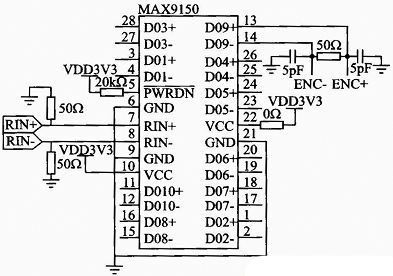

采用LVDS转发器MAX9150转换FPGA所给的时钟信号,作为LTC2207的采集控制信号ENC.MAX9150的转换电路如图2所示。

图2 MAX9150的转换电路

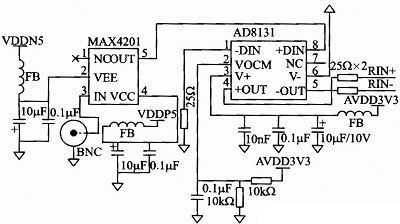

LTC2207的模拟差分信号输入前端的调理芯片采用低噪声、低功耗、超高速开环缓冲器MAX4201和高速差分驱动器AD8131.采集输入信号的前端调理电路如图3所示。图中MAX4201采用±5 V供电,对地并联的电容给电源滤波,为缓冲器提供无干扰的电源。缓冲后的信号,由MAX 4201的5引脚输出,其输出阻抗是50 Ω,再经过AD8131完成单端到差分的转换。

图3 采集输入信号的前端调理电路

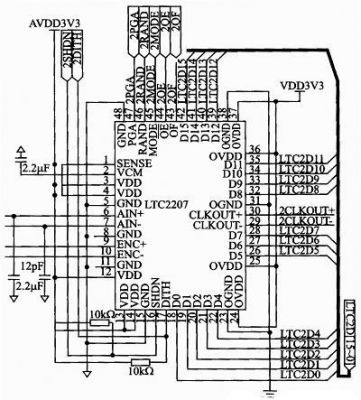

LTC2207的采集控制电路如图4所示。其中,AIN+、AIN-为差分模拟输入信号;ENC+、ENC-为采集芯片的时钟控制信号;D0~D15为16位数据输出信号;CLKOUT+、CLKOUT-为时钟输出信号。

图4 LTC2207的采集控制电路

3 ARM与FPGA的编程控制

采用硬件描述语言Verilog HDL,对LTC2207相关引脚的使能以及FPGA如何读取采集来的数据的程序如下:

S3C2440控制启动FPGA开始采集的STart程序如下:

4 仿真验证

采用QuartusII软件中的调试工具SignalTapII逻辑分析仪进行仿真验证。当采集输入为0.453 V直流量时,FPGA采集的数据仿真如图5所示。

可以观察数据3337h、3333h、332Bh、3337h等变化不大,仅在低5位有所变化。根据A/D采集原理,输入电压/参考电压=采样值/216.所给参考电压是2.25 V,采样值若取以上数据中的3 334h(在相对稳定的数据中任取一个),转换成十进制为13 108,代入以上公式:13108×2.25/65536=0.45.得到FPGA读到的数据计算的输入电压是0.45 V,而此时测得的实际输入电压是0.453 V.误差很小,约为0.6%,基本由噪声所致,采得的数据比较精确。

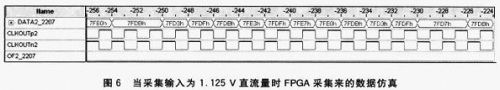

当采集输入为1.125 V直流量时,FPGA采集来的数据仿真如图6所示。同理若取其中的7FE0h,此时算得的误差约为0.8‰。

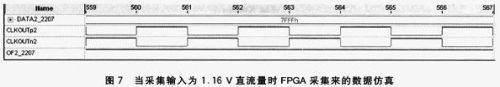

当采集输入为1.16 V直流量时FPGA采集来的数据仿真如图7所示。

从图中可发现此输入下数据已经达到满值(输入超过1.125 V),OF为高,说明数据有溢出。

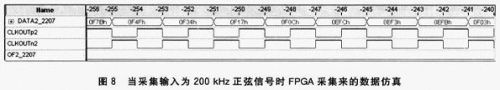

当采集输入是由信号发生器给的200 kHz正弦信号时FPGA采集来的数据仿真如图8所示。

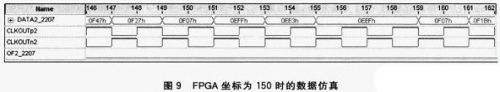

由一个周期采样点数公式N=Tsig/Tsam=fsam/fsig,知此输入频率下采样点数为40 MHz/200 kHz=200,若看坐标-250处的OF17h,则找出一个周期后的那个数是不是和初始值相同。FPGA坐标为150时的数据仿真如图9所示。它处在坐标150的位置为OF07h,和OF17h相差很小。取对应的多组数观察都证明对模拟信号的数据采集亦是比较正确的。

结语

针对A/D转换芯片LTC2207,详细描述了以FPGA和ARM作为控制器的采样设计。采用FPGA直接对A/D进行配置,避免了采用DSP、单片机等进行配置的传统方式,因而设计灵活、简单、通用性强。通过对采集来的数据进行仿真验证,发现在ARM和FPGA的控制下16位A/D芯片LTC2207得到了很好的采集应用。

评论