Cortex-M3可编程片上系统原理及应用

《Cortex-M3可编程片上系统原理及应用》系统化、模块化地介绍了Cypress公司的PSoC5内所集成的ARMCortex-M3CPU硬核处理器结构及指令集、PSoC5内各个功能单元的结构以及基于PSoCCreator2.0软件的片上系统的设计流程。主要内容包括:PSoC设计导论,PSoC5 CPU及存储子系统,PSoC5CPU指令系统,PSoC5公共资源,PSoC编程和调试接口功能,基于PSoCCreator的程序设计,定时器、计数器和PWM模块,LCD显示驱动模块,FC总线模块,USB总线模块,通用数字块UDB,模拟前端模块,ADC和DAC模块,电容感应模块,数字滤波器模块和uC-OS/Ⅲ操作系统。本书可作为从事Cypress可编程片上系统设计的设计人员的参考用书,也可作为大学本科生和研究生教材,同时也可作为Cypress公司相关内容的培训教材。

本文引用地址:http://www.amcfsurvey.com/article/201706/348140.htm

第1章 PSoC设计导论 1

1.1 微控制器基础 1

1.1.1 微控制器的涵义 1

1.1.2 微控制器编程语言 2

1.2 可编程片上系统PSoC概述 3

1.2.1 PSoC发展概述 3

1.2.2 PSoC设计方法 5

1.3 PSoC5设计流程 7

1.3.1 硬件设计流程 8

1.3.2 软件设计流程 9

1.4 PSoC5的结构及功能 10

1.4.1 PSoC5系统结构概述 10

1.4.2 数字子系统结构及功能 10

1.4.3 模拟子系统结构及功能 13

1.4.4 输入/输出引脚功能 14

1.5 PSoC5器件概述 15

1.5.1 PSoC5引脚分布 15

1.5.2 PSoC5器件分类和资源 16

第2章 PSoC5 CPU及存储子系统 19

2.1 Cortex-M3内核结构概述 19

2.1.1 Cortex-M3内核结构特性 19

2.1.2 流水线结构 20

2.1.3 寄存器 20

2.1.4 操作模式 23

2.1.5 SysTick定时器 23

2.1.6 存储器空间映射 23

2.1.7 异常及处理 26

2.2 嵌套向量中断控制器 26

2.2.1 中断控制器的特性 26

2.2.2 中断使能 28

2.2.3 中断优先级 29

2.2.4 电平/脉冲中断 30

2.2.5 中断的执行 30

2.2.6 PSoC5中断特性 31

2.2.7 中断控制器和功耗模式 34

2.3 高速缓存控制器 35

2.4 PHUB和DMA控制器 36

2.4.1 PHUB 36

2.4.2 DMA控制器 38

2.4.3 访问DMAC 44

2.4.4 DMAC传输模式 45

2.4.5 PHUB和DMAC寄存器列表 46

2.5 PSoC5存储器系统 47

2.5.1 SRAM存储器结构及功能 47

2.5.2 非易失性锁存器结构及功能 48

2.5.3 Flash程序存储器结构及功能 49

2.5.4 EEPROM存储器结构及功能 50

第3章 PSoC5 CPU指令系统 51

3.1 Cortex-M3指令寻址模式 51

3.2 Cortex-M3 CPU指令集 53

3.2.1 Cortex-M3指令集概述 53

3.2.2 CMSIS函数 54

3.2.3 存储器访问指令 54

3.2.4 通用数据处理指令 61

3.2.5 乘法和除法指令 69

3.2.6 饱和指令 71

3.2.7 比特位操作指令 72

3.2.8 分支和控制指令 74

3.2.9 杂项操作指令 77

3.3 Cortex-M3 汇编语言编程模型 80

第4章 PSoC5公共资源 82

4.1 时钟管理 82

4.1.1 内部振荡器 83

4.1.2 外部振荡器 84

4.1.3 DSI时钟 86

4.1.4 相位锁相环 86

4.1.5 USB时钟 86

4.2 电源管理 87

4.2.1 电源模式 87

4.2.2 电源监控 89

4.3 看门狗定时器 89

4.4 复位 90

4.4.1 复位模块功能介绍 90

4.4.2 复位源 91

4.5 I/O系统和布线资源 92

4.5.1 I/O系统特性 92

4.5.2 I/O驱动模式 94

4.5.3 DSI控制数字I/O 97

4.5.4 模拟I/O引脚 99

4.5.5 LCD驱动引脚 100

4.5.6 电容感应触摸引脚 100

4.5.7 SIO功能和特性 100

4.5.8 上电时I/O配置 101

4.5.9 过电压容限 101

4.5.10 端口中断控制器单元 102

第5章 PSoC编程和调试接口功能 104

5.1 测试控制器 104

5.1.1 测试控制器结构 104

5.1.2 SWD接口规范 104

5.1.3 PSoC5 SWD的特性 106

5.2 Cortex-M3调试和跟踪 107

5.2.1 内核调试 108

5.2.2 系统调试 109

5.3 非易失性存储器编程 110

第6章 基于PSoC Creator的程序设计 112

6.1 PSoC Creator软件功能 112

6.2 汇编语言GPIO控制程序的设计 113

6.2.1 创建和配置工程 113

6.2.2 查看和设置公共资源 114

6.2.3 编写GPIO汇编语言控制程序 115

6.3 C语言GPIO控制程序的设计 119

6.3.1 使用C语言指针对GPIO端口控制 120

6.3.2 调用API函数对GPIO端口控制 120

6.3.3 PSoC5的SRAM内函数定位 126

6.4 中断服务程序的设计 128

6.4.1 创建和配置工程 128

6.4.2 添加IP核资源到设计 128

6.4.3 IP核参数配置和连接 129

6.4.4 中断服务程序的设计 131

6.4.5 下载并调试工程 133

第7章 定时器、计数器和PWM模块 134

7.1 定时器模块特性 134

7.2 定时器模块结构 134

7.2.1 时钟选择 135

7.2.2 使能/禁止模块 136

7.2.3 输入信号特性 136

7.2.4 操作模式 137

7.2.5 中断使能 141

7.2.6 寄存器列表 141

7.3 PWM控制LED显示的实现 142

7.3.1 创建和配置工程 142

7.3.2 编写软件程序 146

7.3.3 编程及调试 147

第8章 LCD显示驱动模块 148

8.1 LCD的工作原理 148

8.1.1 LCD物理结构 148

8.1.2 LCD液晶分类 149

8.2 LCD驱动特性 154

8.3 LCD驱动系统 154

8.4 LCD功能描述 155

8.4.1 LCD DAC 155

8.4.2 LCD配置选项 156

8.4.3 LCD驱动模块 156

8.4.4 UDB 159

8.4.5 DMA 159

8.5 段式LCD显示的实现 160

8.5.1 段式LCD的功能 160

8.5.2 段式LCD的参数配置 162

8.5.3 编写软件程序 167

8.5.4 编程及调试 169

第9章 I2C总线模块 170

9.1 I2C总线模块概述 170

9.2 I2C总线实现原理 171

9.2.1 I2C总线模块结构 171

9.2.2 典型的I2C数据传输 171

9.2.3 I2C总线寄存器及操作 172

9.3 I2C总线操作模式 173

9.3.1 从模式 173

9.3.2 主模式 174

9.3.3 多主模式 175

9.4 I2C模块通信的实现 176

9.4.1 系统实现原理 176

9.4.2 创建和配置工程 177

9.4.3 编写软件程序 181

9.4.4 编程及调试 183

第10章 USB总线模块 184

10.1 USB总线模块概述 184

10.2 USB模块结构 184

10.2.1 串行接口引擎SIE 185

10.2.2 仲裁器 186

10.3 USB模块工作条件 187

10.3.1 工作频率 187

10.3.2 工作电压 188

10.3.3 收发器 188

10.3.4 端点 188

10.3.5 传输类型 188

10.3.6 中断 189

10.4 逻辑传输模式 189

10.4.1 非DMA访问 190

10.4.2 手工DMA访问 190

10.4.3 控制端点的逻辑传输 193

10.5 PS/2和CMOS I/O模式 194

10.6 USB模块寄存器列表 194

10.7 USB人体学输入设备的实现 195

10.7.1 人体接口设备的原理 195

10.7.2 创建和配置工程 200

10.7.3 编写软件程序 204

10.7.4 编程及调试 205

第11章 通用数字块UDB 207

11.1 通用数字块概述 207

11.2 UDB模块结构 208

11.2.1 PLD模块结构及宏单元 208

11.2.2 数据通道模块 209

11.2.3 状态和控制模块 212

11.3 交通灯控制电路的设计与实现 213

11.3.1 交通灯设计原理 213

11.3.2 交通灯控制电路的设计 213

11.3.3 引脚分配 218

11.3.4 设计下载与测试 218

11.4 静态时序分析 218

第12章 模拟前端模块 220

12.1 模拟比较器 220

12.1.1 输入和输出接口 220

12.1.2 LUT 220

12.2 运算放大器模块 221

12.3 可编程SC/CT模块 223

12.3.1 单纯的放大器 224

12.3.2 单位增益 225

12.3.3 可编程增益放大器 225

12.3.4 互阻放大器 227

12.3.5 连续时间混频器 228

12.3.6 采样混频器 228

12.3.7 Δ-Σ调制器 230

12.3.8 跟踪和保持放大器 231

12.4 精密参考源 231

12.5 基于混频器的精确整流实现 233

12.5.1 整流器设计原理 233

12.5.2 创建和配置工程 233

12.5.3 编写软件程序 237

12.5.4 编程及调试 237

第13章 ADC和DAC模块 238

13.1 Δ-ΣADC模块 238

13.1.1 Δ-ΣADC模块概述 238

13.1.2 Δ-ΣADC结构 239

13.1.3 Δ-Σ ADC操作模式 241

13.2 SAR ADC模块 242

13.2.1 SAR ADC模块概述 242

13.2.2 SAR ADC模块的工作原理 242

13.3 DAC模块 243

13.4 基于SAR ADC的数字电压表实现 246

13.4.1 创建和配置工程 246

13.4.2 编写软件程序 249

13.4.3 编程及调试 250

13.5 基于Δ-Σ ADC的数字电压表实现 251

13.5.1 创建和配置工程 251

13.5.2 编写软件程序 253

13.5.3 编程及调试 254

13.6 IDAC值显示的实现 254

13.6.1 创建和配置工程 255

13.6.2 编写软件程序 258

13.6.3 编程及调试 258

第14章 电容感应模块 259

14.1 电容感应模块的结构 259

14.2 电容感应Δ-Σ算法 262

14.3 电容感应触摸的实现 263

14.3.1 创建和配置工程 263

14.3.2 编写软件程序 266

14.3.3 编程及调试 267

第15章 数字滤波器模块 268

15.1 数字滤波器模块概述 268

15.2 数字滤波器模块结构 269

15.2.1 控制器 269

15.2.2 FSM RAM 270

15.2.3 数据通道 272

15.2.4 地址计算单元 273

15.2.5 总线接口和寄存器描述 274

15.3 基于DFB的数字滤波器实现 276

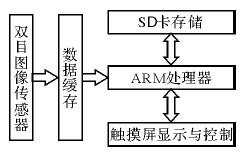

15.3.1 系统结构概述 276

15.3.2 元件参数配置 276

15.3.3 DMA配置向导 280

15.3.4 编写软件程序 282

15.3.5 编程及调试 283

第16章 μC-OS/III操作系统 284

16.1 μC-OS/III操作系统概述 284

16.1.1 操作系统的作用 284

16.1.2 μC-OS/III操作系统内核特征 285

16.1.3 μC/OS-III操作系统文件的结构 288

16.1.4 μC/OS-III操作系统应用程序结构分析 289

16.2 μC-OS/III操作系统内核及功能 296

16.2.1 单任务和多任务处理 296

16.2.2 临界区 300

16.2.3 任务管理 300

16.2.4 准备列表 301

16.2.5 调度 301

16.2.6 上下文切换 302

16.2.7 中断管理 302

16.2.8 等待列表 303

16.2.9 时间管理 303

16.2.10 定时器管理 303

16.2.11 资源管理 304

16.2.12 消息传递 305

16.2.13 多个对象等待处理 307

16.2.14 存储器管理 308

16.3 PSoC5硬件系统的构建 309

16.4 添加中断代码到ISR中 310

16.4.1 添加中断代码到ProbeUART_TxISR.c中 310

16.4.2 添加中断代码到ProbeUART_RxISR.c中 311

16.5 配置引脚 311

16.6 运行设计 312

16.7 启动μC/Probe工具 313

参考文献 316

评论