高级RF收发器满足SDR应用的需求

令人惊讶、有时扑朔迷离的一系列无线标准,具有不同的频率、带宽、协议和格式,为用户带来了前所未有的连接性和访问性。但是同时,它也意味着无线系统工程师在设计或调查问题、性能和选项等过程中面临着严峻的考验。

解决途径似乎很明确:尽可能减少专用硬件的使用,并且以软件定义无线电(SDR)方案取而代之,以便尽可能实现与管理更多的发送和接收功能。目前市场上的高性能、低功耗处理器(包括FPGA)以及它们高速执行复杂算法的能力,使这类实时方案得以实现。

但该解决方案有一个现实的阻碍:很难为接收器和发送器信号路径设计宽带模拟电路。因此,大部分宽带SDR使用了一组重叠、平行的模拟通道,每通道均针对整体 频段内的特定片段优化,同时每个片段内的带宽与目标信号相匹配。虽然这种方法在技术上是可行的,但实现该技术所需的硬件、PC板面积、功耗都十分可观—— 当然还有成本。

这便是Epiq Solutions公司(伊利诺伊州绍姆堡镇)开发其最新SDR单元——Maveriq多通道可重配置RF收发器(见图1)——时所面临的窘况。该收发器 是一款结合了多个RF收发器,用于数据记录的内置固态硬盘(SSD),板载运行Linux的Intel x86 CPU,以及用于高速数据访问的千兆以太网接口的先进平台。它以小封装提供出色的SDR能力,并且覆盖100MHz至6GHz调谐范围。作为针对任务关键 型应用的先进、可重配置无线电系统的设计者和构建者,该公司目标是提供比现有Matchstiq SDR更强大的多通道版本产品。

图1:Maveriq多通道可重新配置RF收发器。

尽 管具有先进的特性和功能,Maveriq却是一款便携式低功耗平台,而之前的解决方案都需要大量繁重的硬件配置。Maveriq结合了可立即运行的专业软 件应用库,能够即刻投入使用,解决棘手的信号处理要求。这些要求包括:扫描和解码来自基站及手机的蜂窝无线电信号;在内部硬盘(SSD)上记录宽带RF以 及RF回放信号;实现2×2多输入多输出(MIMO)波形。

提供新的设计方法

专为SDR应用量身定制的全新IC——ADI的RF捷变收发器AD9361——得以让 Epiq公司的工程师将如此多的功能封装在一个小型、低功耗单元中。Epiq CEO兼系统架构师John Orlando表示:“AD9361为我们提供了新一代SDR平台所需的RF灵活性与集成度。”

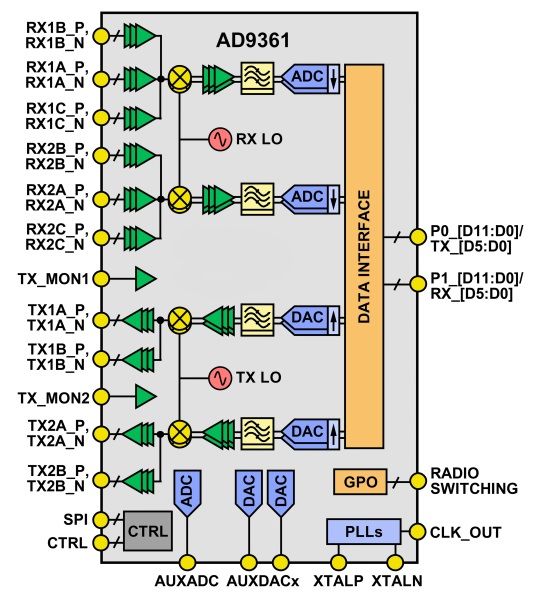

这款10mm×10mm芯片 级器件集成了双独立通道(如图2所示),具有200kHz至56MHz用户可调谐带宽,以及工作速率高达61.44MSPS的12位ADC与DAC,另外 还提供建立70MHz至6GHz信号链所需的其他特性与性能。用户可实时调节关键的工作参数,以便尽量匹配应用要求。使用该器件可缩小整个模拟前端(AFE)的整体尺寸,同时将这部分设计的功耗保持在1W范围内,即保持在产品功耗预算范围内。

图2:ADI公司AD9361 RF捷变收发器IC框图。

整个Maveriq单元(如图3所示)采用一对AD9361即可支持2×2 MIMO或4通道接收器配置,RF调谐范围为100MHz至6GHz,步进大小为1kHz,调谐时间为2ms。该单元包括:性能为1PPS的集成式GPS 接收器,支持100MB/s以上(持续)数据记录速率、容量高达1TB的内部SSD,以及与外部系统接口的千兆以太网。

图3:Maveriq单元简化系统框图。

处理功能集中在运行Linux的双核Intel x86 CPU和用于信号处理任务的FPGA,连同实时可加载/可执行软件应用程序,所有这些都由针对应用定制的软件开发套件(SDK)提供支持。整个单元尺寸仅 为9.1×6.6×1.7(23cm×16.7cm×4.3cm),重1.9lb(0.9kg),功耗为15W(取决于FPGA和I/O使用情 况)。

当然,合适的RF性能才可充分发挥处理能力。接收器的典型噪声系数低于8dB,典型IIP3为–10dBm。发送端性能参数(如带宽、调谐和速度)可补偿接收端数目,并且输出功耗为+5dBm。

虽然AD9361 IC是实现该设计的关键,但总能实现进一步的性能改善。某些应用要求将RF性能向下延展至20MHz及更低的范围,这超出了AD9361能够处理的范围。另外,选择可在低至20MHz工作的RF元器件(比如低噪声放大器,LNA) 同样有一定的难度,尤其是尺寸和功耗受限型设计。通常,人们会认为,低功耗处理技术的进步配合大容量存储器产品,再加上高速数字I/O和连接(全部由摩尔 定律所推动)对于小型、高性能SDR而言已经足够。而事实上,用于接收路径和发送路径的前端通道具有同等的重要性,并且,兼有模拟处理、滤波和转换的RF IC的发展不仅最大程度降低了算法的负担,同时还能实现大部分SDR的实际性能。

评论