手机储存的未来:eMMC快速转向UFS

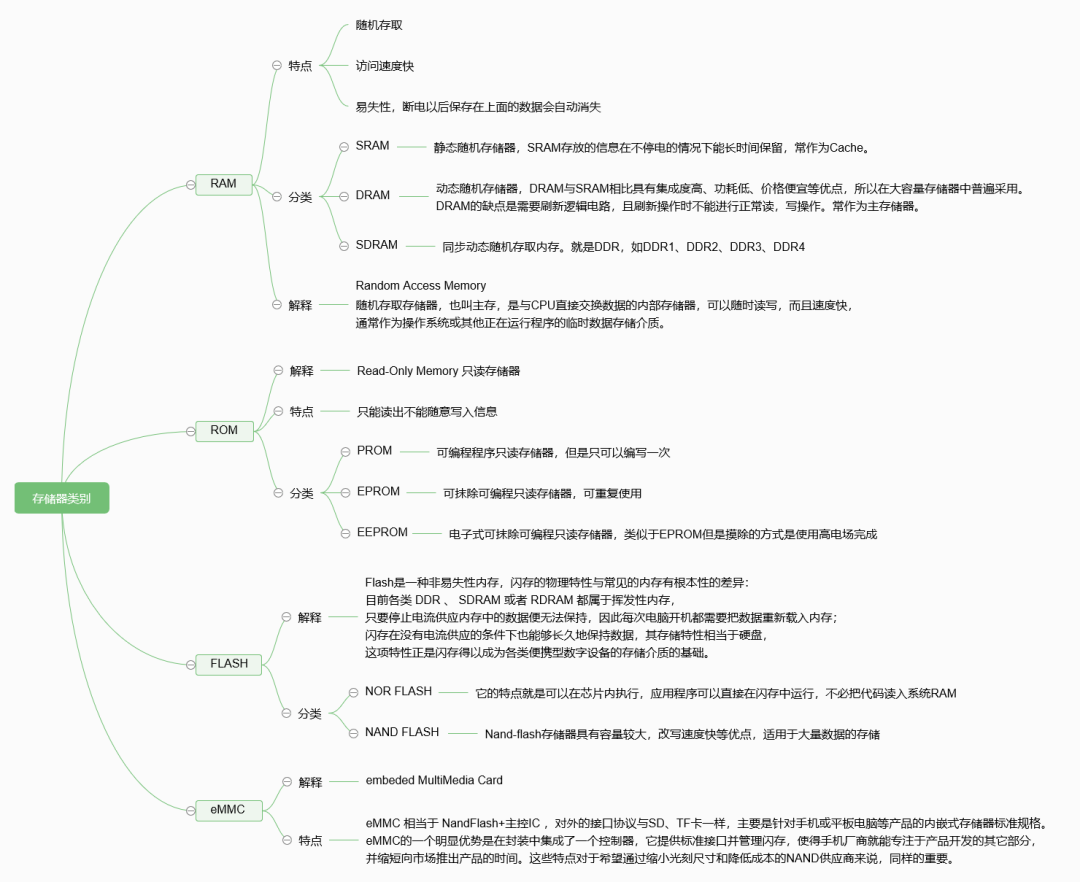

随着游戏与视讯应用在行动装置上的普及,以及手机处理器性能的提升,eMMC的性能已经不能满足行动装置对于内存读写性能的要求,新一代的通用闪存储存(UFS)规格应运而生。

本文引用地址:http://www.amcfsurvey.com/article/201704/358283.htm在高速数字接口中,并行总线越来越少。 原因很简单,随着系统频率的提升,并行总线在板级建置时已经遭遇到实体瓶颈,抖动、串扰、讯号偏移、传输路径不完美等因素,都将大幅降低并行总线持续建立时间窗口,从而限制系统带宽的进一步提升。

在高速串行/解串器(Serdes)技术取得突破后,新式串行总线越来越流行,以USB和PCIe为代表的串行总线在板级以串行方式连接、在芯片内部将数据译码成平行数据,从而使得板级数据线路之间的关系去耦合,既大幅降低了板级布线难度,又突破了系统带宽限制。 因此,新式串行总线正如火如荼地进展,在个人计算机(不含工控与特殊用途计算机)领域,PCIe接口已经完全取代PCI接口,SATA接口也完全取代了PATA接口。

不过,在手机储存接口方面,嵌入式多媒体卡(eMMC)规格的市占率仍然较高,原因之一是行动装置对于储存性能的要求较个人计算机(PC)更低。 然而,随着游戏与视讯应用在行动装置上的普及,以及手机处理器性能的提升,eMMC的性能已经不能满足行动装置对于内存读写性能的要求,新一代的通用闪存储存(UFS)规格应运而生。

UFS的性能优势

多媒体卡(MMC)标准于1997年问世,说来有趣,MMC最初的标准就是一根数据线,后来扩展到8根数据线,eMMC标准则将闪存晶粒和控制器放入更紧密的球门阵列(BGA)封装,以适应行动装置对封装尺寸的要求。 首批eMMC产品于2007年正式推向市场,到目前为止,JEDEC的最新标准为eMMC 5.1。

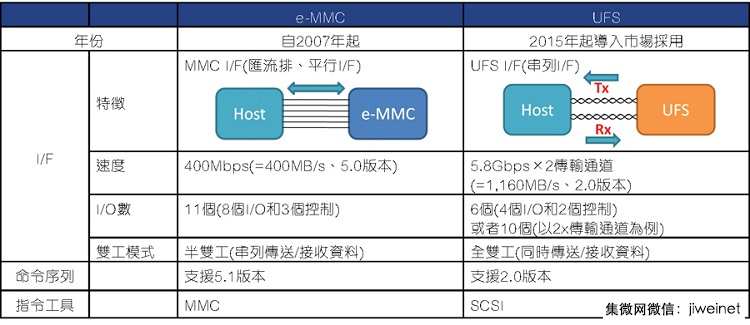

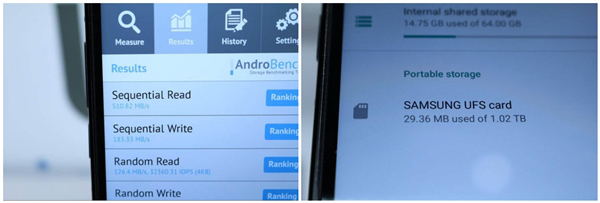

如前所述,并行总线在速度增加到一定值时将无法满足时序要求,eMMC标准单根数据线的极限速度为400Mbps左右,8位数据线标准eMMC接口一次传输峰值速度为400兆字节每秒(400MB/s)。 相形之下,UFS2.0单信道峰值速度为5.8Gpbs,现有标准为双信道,所以速度可达1,160MB/s,将近eMMC标准的3倍。

图1:e-MMC与UFS接口比较

而且,由于eMMC是半双工模式,主、从装置之间数据不能同时互动,而UFS是全双工模式,便于传输性能的提升。 所以采用UFS接口的系统启动时间更快,读写响应也更迅速。 根据东芝(Toshiba)的数据,在连续读取、随机读取、连续写入与随机写入等操作中,UFS 2.1产品基本能够达到eMMC 5.1产品的1-3倍。 UFS新一代标准还将大幅提高读写性能,但eMMC性能再提升的空间并不大。

UFS规格以先进的Serdes技术为基础,其读写性能的大幅提升并未以大量增加功耗为代价。 由于UFS讯号电压摆幅只有200毫伏(mV),而eMMC标准是1.8伏(V)或3.3V,因此两种产品待机功耗相差无几,而且从第三代到第五代,东芝的每一代UFS产品功耗水平都得到了提升。

从eMMC转向UFS接口

从并行总线换到串行总线,减少了高速数据线的连接,简化了硬件工程师的工作。

以东芝的产品为例,UFS封装与eMMC封装一致,用户可以选择对应的封装直接取代。 相较于第三代UFS产品使用三电源供电,东芝的第四代与第五代UFS产品不必再使用1.2V电源,从而使内存模块的电源设计更简单。

图2:第四代以后的UFS内存只需要两个电源

在韧体层面,相较于eMMC产品,新一代的UFS产品已经将除错、坏块管理、损耗平衡以及垃圾回收等功能一并封装,为用户在闪存应用开发上节省了大量的时间。

为了方便用户除错,有些UFS产品还提供了板级除错接脚。 以东芝第5代UFS产品为例,用户只需将2个除错接脚连接到PCB的除错工具接口即可,不需要额外增加电阻电容。 而当出现问题时,用户只需利用除错工具透过这2个接脚连到UFS内存上进行除错。

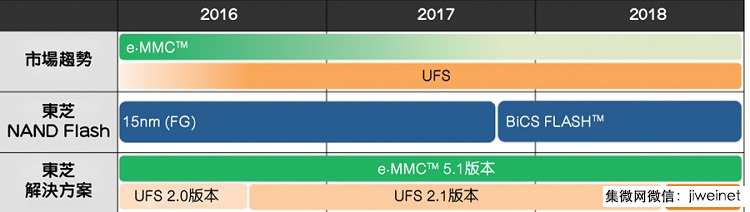

既然UFS较eMMC的性能更大幅提升,更换设计又不复杂,那么当UFS产品成熟时,产品替代进程将非常快。 根据东芝对市场的预测,2017年上半年的旗舰型手机将普遍采用UFS接口。 从2017年下半年开始,中阶手机也将逐步改用UFS闪存,UFS接口在高阶平板中的普及率也将过半。

图3:UFS市场前景

从东芝UFS产品发展蓝图来看,UFS 2.0与2.1产品均已经量产,新一代UFS接口的研发也紧锣密鼓,预期UFS市场的成长曲线将非常陡峭,eMMC在行动装置领域的历史使命已经完成,UFS的时代即将来临。

评论