通信系统中接收链的差分滤波器设计(下)

接上篇

5 带通滤波器设计

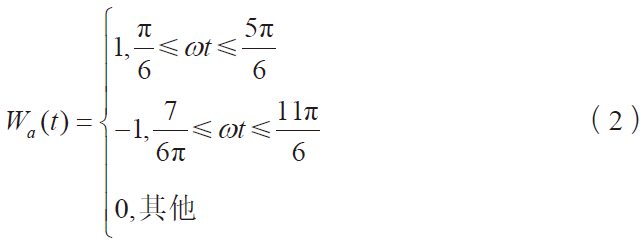

在通信系统中,当IF频率相当高时,某些低频杂散也 需要滤除,例如半IF杂散。对于此类应用,应设计带通滤波 器。对于带通滤波器,低频抑制和高频抑制不必对称。设计 带通抗混叠滤波器的简单方法是先设计一个低通滤波器,然

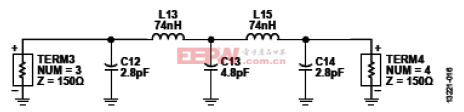

图18 单端低通滤波器

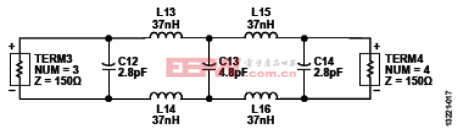

图19 采用理想元件的差分低通滤波器

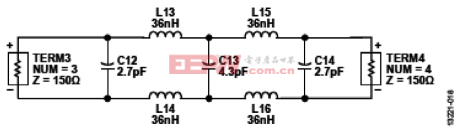

图20 采用实际值的差分低通滤波器 图21 差分带通滤波器

图21 差分带通滤波器

后在滤波器最后一级的分流电容上并联一个分流电感,用以

限制低频成分(分流电感是一个高通谐振极点)。如果一级 高通电感还不够,可在第一级分流电容上再并联一个分流电 感,从而更好地抑制低频杂散。增加分流电感之后,再次调 谐所有元件以获得正确的带外抑制规格,然后最终确定滤波 器元件值。

注意,对于带通滤波器,一般不建议使用串联电容, 因为这会增加调谐和调试的难度。电容值通常相当小,会受 到寄生电容很大的影响。

6 应用示例

本部分说明一个位于ADL5201和AD6641之间的滤波器 设计应用示例。ADL5201是一款高性能IF数字控制增益放 大器(DGA),针对基站实IF接收机应用或数字预失真(DPD) 观测路径而设计,具有30 dB增益控制范围,线性度极高, OIP3达到50 dBm,电压增益约为20 dB。AD6641是一款250

MHz带宽DPD观测接收机,集成一个12位500 MSPS ADC、 一个16000 × 12 FIFO和一个多模式后端,允许用户通过串 行端口检索数据。该滤波器示例是一个DPD应用。

下面是取自一个实际通信系统设计的一些带通滤波器 设计规格:

• 中心频率: 368.4 MHz

• 带宽: 240 MHz;

• 输入和输出阻抗:

150 Ω ;

• 带内纹波: 0.2 dB;

图22 使用弯曲校正

图23 避免90°弯曲

图24 避免走线分支

图25 对称布线指南

• 带外抑制:30 dB (614.4 MHz) 。

要完成该示例设计,请执行以下步骤:

• 插入损耗: 1 dB ;

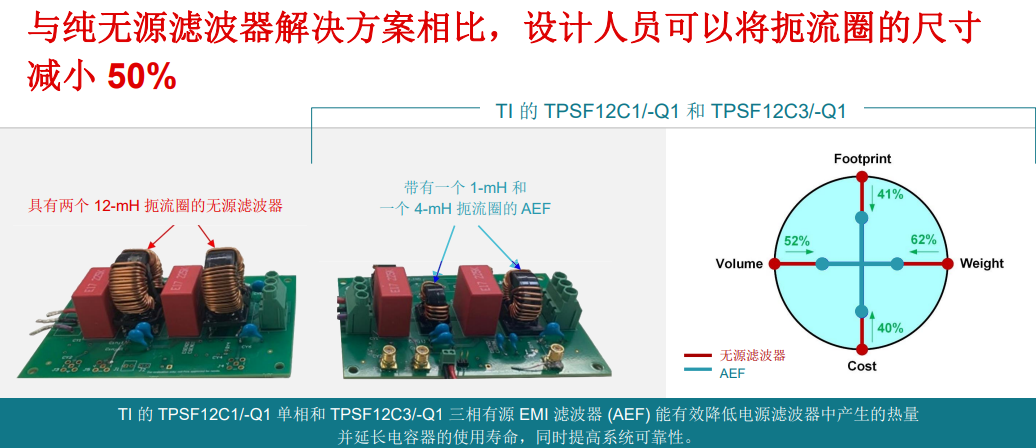

1. 从单端低通滤波器设计开始(参见图18)。

2. 将单端滤波器变为差分滤波器。源阻抗和负载阻抗 保持不变,所有电容并联,所有串联电感减半并放在另一差 分路径中(参见图19)。

3. 用实际值优化元件的理想值(参见图20)。

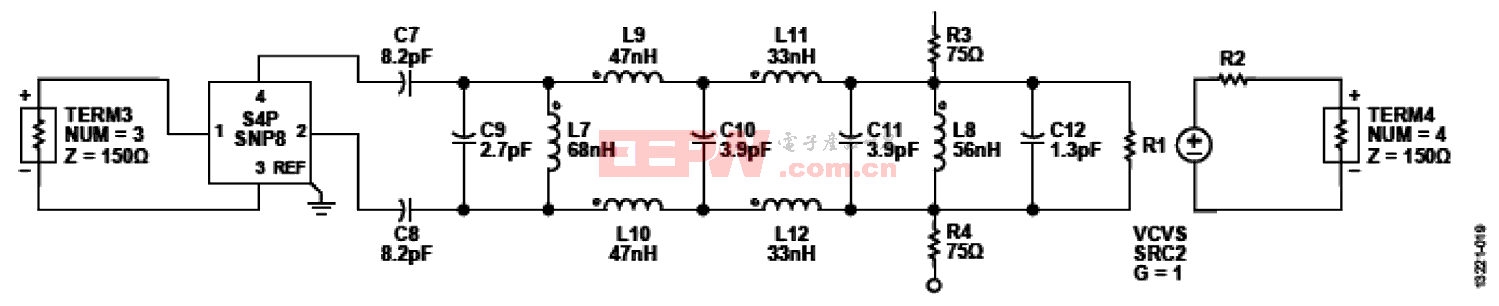

4. 对于子系统级仿真,应在输入端增加ADL5201 DGA S - 参 数 文 件 , 并 使 用 压 控 电 压 源 来 模 拟 滤 波 器 输 出 端 的 AD6641 ADC。 为

将低通滤波器变为 带通滤波器,增加 两 个 分 流 电 感 : L 7 与 C 9 并 联 , L 8 与 C 1 1 并 联 。 C 1 2

代 表 A D 6 6 4 1 输 入

图26 差分电路PCB布局设计示例

电 容 。 R 3 和 R 4 是放在AD6641输入端的两个负载电阻,用作滤波器的负载。AD6641输入为高阻抗。调谐后的情况参见图21。

5. 采用理想元件的仿真结构如图16所示。

6. 用目标器件(例如Murata LQW18A)的电感S-参数文 件代替所有理想电感。插入损耗比使用理想电感略高。仿真 结果略有变化,如图17所示。

7 差分滤波器布局考虑

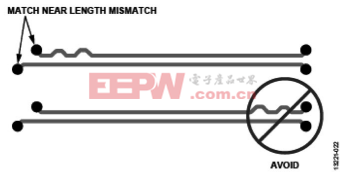

成对差分走线的长度须相同。此规则源自这一事实:

差分接收器检测正负信号跨过彼此的点,即交越点。因此,信号须同时到达接收器才能正

常工作。

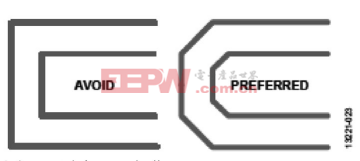

差 分 对 内 的 走 线 布 线 须 彼此靠近,如果一对中的相邻 线路之间的距离大于电介质厚 度的2倍,则其间的耦合会很 小。此规则也是基于差分信号 相等但相反这一事实,如果外 部噪声同等地干扰两个信号, 则其影响会互相抵消。同样, 如果走线并排布线,则差分信 号在相邻导线中引起的任何干扰噪声都会彼此抵消。同一差分对内的走线间距在全长范围内须保持不变。

如果差分走线彼此靠近布线,则会影响总阻抗。如果此间距 在驱动器与接收器之间变化不定,则一路上会存在阻抗不匹 配,导致反射。

差分对之间的间距应较宽,以使其间的串扰最小。

如果在同一层上使用铜填充,应加大从差分走线到铜 填充之间的间隙。推荐最小间隙为走线到铜填充的走线宽度 的3倍。

在靠近差分对内偏斜源处引入少量弯弯曲曲的校正,

从而降低这种偏斜(参见图22)。 差分对布线时,应避免急转弯(90°)(参见图23)。 差分对布线时,应使用对称布线(参见图25)。 若需要测试点,应避免引入走线分支,而且测试点应

对称放置(参见图24)。

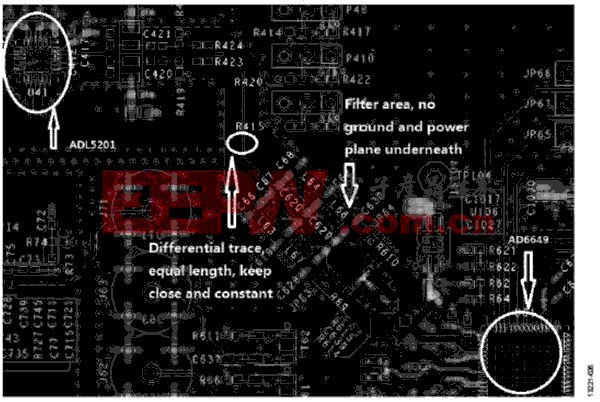

考 虑 降 低 对 滤 波 器 元 件 值 的 要 求 , 减 少 印 刷 电 路 板 (PCB)上的调谐工作量;寄生电容和电感应尽可能小。与滤 波器设计中的电感设计值相比,寄生电感可能微不足道。寄 生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只 有几pF,如果寄生电容达到数十分之一pF,滤波器响应就 会受到相当大的影响。为了避免寄生电容影响,一个良好的 做法是避免差分布线区域和电源扼流圈下有任何接地或电源 层。

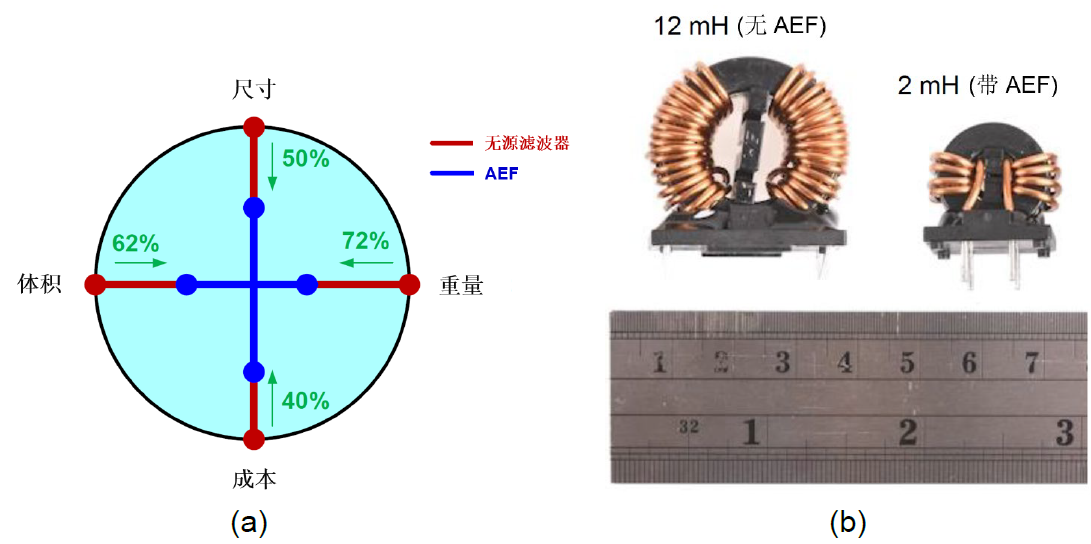

ADI公司接收器参考设计板(参见图26)提供了差分滤 波器PCB布局的一个示例。图26显示ADL5201和AD6649之间 有一个五阶滤波器。AD6649是一款14位250 MHz流水线式 ADC,具有非常好的SNR性能。

评论