加法器是什么?加法器电路原理

加法器 :

本文引用地址:http://www.amcfsurvey.com/article/201611/340533.htm加法器是为了实现加法的。

即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

对于1位的二进制加法,相关的有五个的量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。前三个量为输入量,后两个量为输出量,五个量均为1位。

对于32位的二进制加法,相关的也有五个量:1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。而最后的第32位必须在前31位全部计算出结果后,才能开始计算。这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

可以看出,上法是将32位的加法1位1位串行进行的,要缩短进行的时间,就应设法使上叙进行过程并行化。

逐位进位加法器,在每一位的计算时,都在等待前一位的进位。那么不妨预先考虑进位输入的所有可能,对于二进制加法来说,就是0与1两种可能,并提前计算出若干位针对这两种可能性的结果。等到前一位的进位来到时,可以通过一个双路开关选出输出结果。这就是进位选择加法器的思想。

提前计算多少位的数据为宜?同为32位的情况:线形进位选择加法器,方法是分N级,每级计算32/N位;平方根进位选择加法器,考虑到使两个路径(1,提前计算出若干位针对这两种可能性的结果的路径,2,上一位的进位通过前面的结构的路径)的延时达到相等或是近似。方法,或是2345666即第一级相加2位,第二级3位,第三级4位,第四级5位,第五级6位,第六级6位,第七级6位;或是345677即第一级相加3位,第二级4位,第三级5位,第四级6位,第五级7位,第六级7位。

进一步分析加法进行的机制,可以使加法器的结构进一步并行化。

令G = AB,P = A⊕B,则COUT(G,P) = G + PCIN,S(G,P)=P⊕CIN。由此,A,B,CIN,S,COUT五者的关系,变为了G,P,CIN,S,COUT五者的关系。

再定义点运算(•),(G,P)•(G’,P’)=(G + PG’,PP’),可以分解(G 3:2,P3:2) =(G3,P3)•(G2,P2)。 点运算服从结合律,但不符合交换律。

点运算只与G,P有关而与CIN无关,也就是可以通过只对前面若干位G,P进行点运算计算,就能得到第N位的GN:M,PN:M值,当取M为0时,获得的GN:0,PN:0即可与初使的CIN一起代入COUT(G,P) = G + PCIN,S(G,P)=P⊕CIN,得到此位的COUT,S;而每一位的G,P值又只与该位的A,B值即输入值有关,所以在开始进行运算后,就能并行的得到每一位的G,P值。

以上分析产生了超前进位加法器的思想:三步运算,1,由输入的A,B算出每一位的G,P;2,由各位的G,P算出每一位的GN:0,PN:0;3,由每一位的GN:0,PN:0与CIN算出每一位的COUT,S。其中第1,3步显然是可以并行处理的,计算的主要复杂度集中在了第2步。

第2步的并行化,也就是实现GN:0,PN:0的点运算分解的并行化。

加法器定义

实现多位二进制数相加的电路称为加法器, 它能解决二进制中1+1=10 的功能(当然还有 0+0、0+1、1+0).

加法器的分类

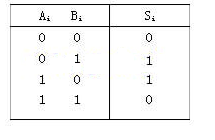

一、半加器概念:能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

Ai、Bi:加数, Si:本位的和。

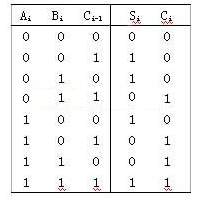

二、全加器

概念:能对两个1位二进制数进行相加并考虑低位来的进位,即相当于3个1位二进制数相加,求得和及进位的逻辑电路称为全加器。或:不仅考虑两个一位二进制数相加,而且还考虑来自低位进位数相加的运算电路,称为全加器。

Ai、Bi:加数, Ci-1:低位来的进位,Si:本位的和, Ci:向高位的进位。

加法器的实现

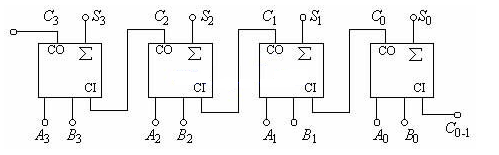

1、串行进位加法器

构成:把n位全加器串联起来,低位全加器的进位输出连接到相邻的高位全加器的进位输入。

特点:进位信号是由低位向高位逐级传递的,速度不高。

2、并行进位加法器(超前进位加法器)

设一个n位的加法器的第i位输入为ai、bi、ci,输出si和ci+1,其中ci是低位来的进位,ci+1(i=n-1,n-2,…,1,0)是向高位的进位,c0是整个加法器的进位输入,而cn是整个加法器的进位输出。则和 si=ai i i+ ibi i+ i ici+aibici (1)

进位ci+1=aibi+aici+bici (2)

令gi=aibi, (3)

pi=ai+bi, (4)

则 ci+1= gi+pici (5)

只要aibi=1,就会产生向i+1位的进位,称g为进位产生函数;同样,只要ai+bi=1,就会把ci传递到i+1位,所以称p为进位传递函数。把(5)式展开,得到

ci+1= gi+ pigi-1+pipi-1gi-2+…+ pipi-1…p1g0+ pipi-1…p0c0 (6) 随着位数的增加(6)式会加长,但总保持三个逻辑级的深度,因此形成进位的延迟是与位数无关的常数。一旦进位(c1~cn-1)算出以后,和也就可由(1)式得出。

使用上述公式来并行产生所有进位的加法器就是超前进位加法器。产生gi和pi需要一级门延迟,ci 需要两级,si需要两级,总共需要五级门延迟。与串联加法器(一般要2n级门延迟)相比,(特别是n比较大的时候)超前进位加法器的延迟时间大大缩短了。

评论