MCS-51单片机的引脚描述及片外总线结构

HMOS制造工艺的MCS-51单片机都采用40引脚的直插封装(DIP方式),制造工艺为CHMOS的80C51/80C31芯片除采用DIP封装方式外,还采用方型封装工艺,引脚排列如图。其中方型封装的CHMOS芯片有44只引脚,但其中4只引脚(标有NC的引脚1、12、23、34)是不使用的。在以后的讨论中,除有特殊说明以外,所述内容皆适用于CHMOS芯片。

如图,是MCS-51的逻辑符号图。在单片机的40条引脚中有2条专用于主电源的引脚,2条外接晶体的引脚,4条控制或与其它电源复用的引脚,32条输入/输出(I/O)引脚。

下面按其引脚功能分为四部分叙述这40条引脚的功能。

1、主电源引脚VCC和VSS

VCC——(40脚)接+5V电压;

VSS——(20脚)接地。

2、外接晶体引脚XTAL1和XTAL2

XTAL1(19脚)接外部晶体的一个引脚。在单片机内部,它是一个反相放大器的输入端,这个放大器构成了片内振荡器。当采用外部振荡器时,对HMOS单片机,此引脚应接地;对CHMOS单片机,此引脚作为驱动端。

XTAL2(18脚)接外晶体的另一端。在单片机内部,接至上述振荡器的反相放大器的输出端。采用外部振荡器时,对HMOS单片机,该引脚接外部振荡器的信号,即把外部振荡器的信号直接接到内部时钟发生器的输入端;对XHMOS,此引脚应悬浮。

3、控制或与其它电源复用引脚RST/VPD、ALE/PROG、PSEN和EA/VPP

①RST/VPD(9脚)当振荡器运行时,在此脚上出现两个机器周期的高电平将使单片机复位。推荐在此引脚与VSS引脚之间连接一个约8.2k的下拉电阻,与VCC引脚之间连接一个约10μF的电容,以保证可靠地复位。

VCC掉电期间,此引脚可接上备用电源,以保证内部RAM的数据不丢失。当VCC主电源下掉到低于规定的电平,而VPD在其规定的电压范围(5±0.5V)内,VPD就向内部RAM提供备用电源。

②ALE/PROG(30脚):当访问外部存贮器时,ALE(允许地址锁存)的输出用于锁存地址的低位字节。即使不访问外部存储器,ALE端仍以不变的频率周期性地出现正脉冲信号,此频率为振荡器频率的1/6。因此,它可用作对外输出的时钟,或用于定时目的。然而要注意的是,每当访问外部数据存储器时,将跳过一个ALE脉冲。ALE端可以驱动(吸收或输出电流)8个LS型的TTL输入电路。

对于EPROM单片机(如8751),在EPROM编程期间,此引脚用于输入编程脉冲(PROG)。

③PSEN(29脚):此脚的输出是外部程序存储器的读选通信号。在从外部程序存储器取指令(或常数)期间,每个机器周期两次PSEN有效。但在此期间,每当访问外部数据存储器时,这两次有效的PSEN信号将不出现。PSEN同样可以驱动(吸收或输出)8个LS型的TTL输入。

④EA/VPP(引脚):当EA端保持高电平时,访问内部程序存储器,但在PC(程序计数器)值超过0FFFH(对851/8751/80C51)或1FFFH(对8052)时,将自动转向执行外部程序存储器内的程序。当EA保持低电平时,则只访问外部程序存储器,不管是否有内部程序存储器。对于常用的8031来说,无内部程序存储器,所以EA脚必须常接地,这样才能只选择外部程序存储器。

对于EPROM型的单片机(如8751),在EPROM编程期间,此引脚也用于施加21V的编程电源(VPP)。

4、输入/输出(I/O)引脚P0、P1、P2、P3(共32根)

①P0口(39脚至32脚):是双向8位三态I/O口,在外接存储器时,与地址总线的低8位及数据总线复用,能以吸收电流的方式驱动8个LS型的TTL负载。

②P1口(1脚至8脚):是准双向8位I/O口。由于这种接口输出没有高阻状态,输入也不能锁存,故不是真正的双向I/O口。P1口能驱动(吸收或输出电流)4个LS型的TTL负载。对8052、8032,P1.0引脚的第二功能为T2定时/计数器的外部输入,P1.1引脚的第二功能为T2EX捕捉、重装触发,即T2的外部控制端。对EPROM编程和程序验证时,它接收低8位地址。

③P2口(21脚至28脚):是准双向8位I/O口。在访问外部存储器时,它可以作为扩展电路高8位地址总线送出高8位地址。在对EPROM编程和程序验证期间,它接收高8位地址。P2可以驱动(吸收或输出电流)4个LS型的TTL负载。

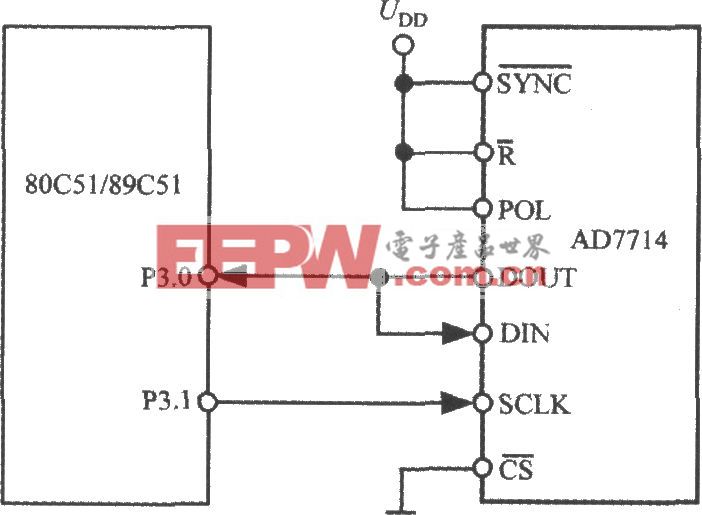

④P3口(10脚至17脚):是准双向8位I/O口,在MCS-51中,这8个引脚还用于专门功能,是复用双功能口。P3能驱动(吸收或输出电流)4个LS型的TTL负载。

作为第一功能使用时,就作为普通I/O口用,功能和操作方法与P1口相同。

作为第二功能使用时,各引脚的定义如表所示。

值得强调的是,P3口的每一条引脚均可独立定义为第一功能的输入输出或第二功能。

表

口线

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

二、MCS-51单片机的片外总线结构

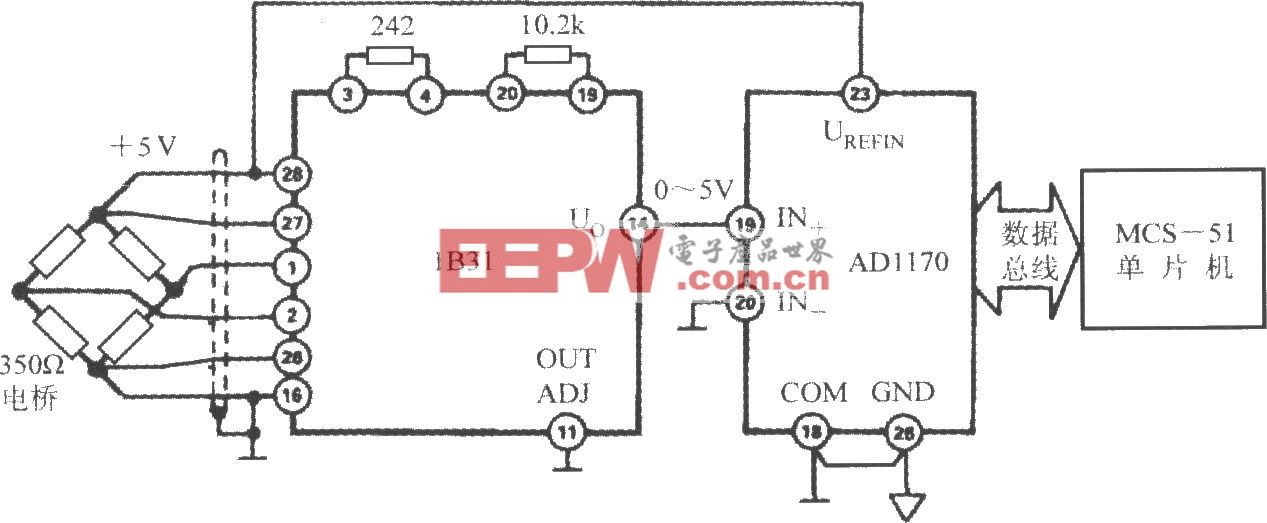

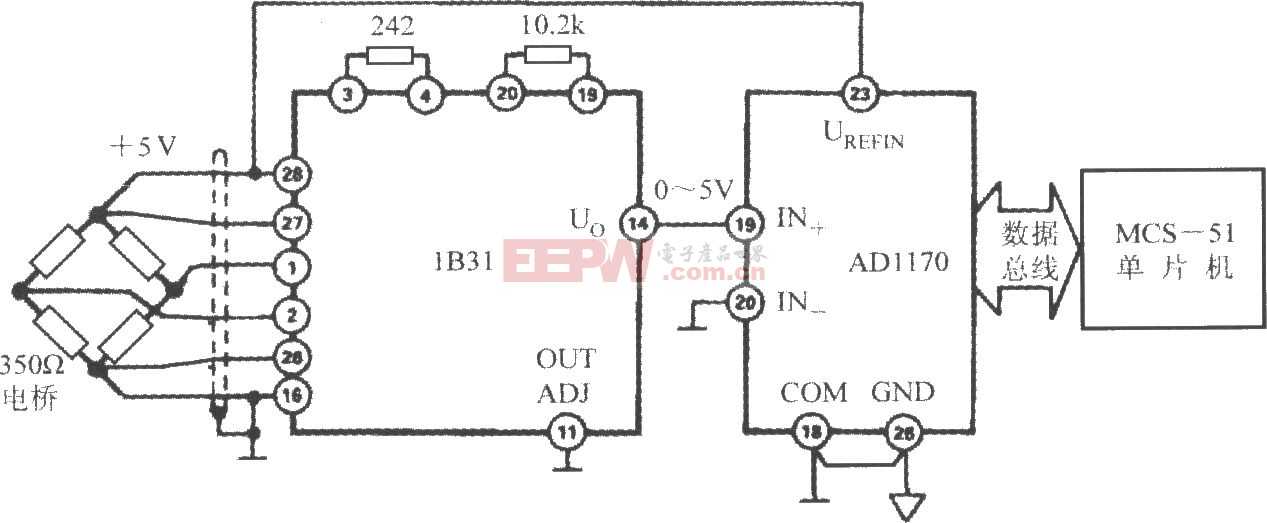

综合上面的描述可知,I/O口线都不能当作用户I/O口线。除8051/8751外真正可完全为用户使用的I/O口线只有P1口,以及部分作为第一功能使用时的P3口。如图,是MCS-51单片机按引脚功能分类的片外总线结构图。

由图我们可以看到,单片机的引脚除了电源、复位、时钟接入,用户I/O口外,其余管脚是为实现系统扩展而设置的。这些引脚构成MCS-51单片机片外三总线结构,即:

①地址总线(AB):地址总线宽为16位,因此,其外部存储器直接寻址为64K字节,16位地址总线由P0口经地址锁存器提供8位地址(A0至A7);P2口直接提供8位地址(A8至A15)。

②数据总线(DB):数据总线宽度为8位,由P0提供。

③控制总线(CB):由P3口的第二功能状态和4根独立控制线RESET、EA、ALE、PSEN组成。

下表列出各个子系列的配制情况供读则参考。

芯片种类

ROM/EPROM

8051(8751,8031)

8052(8752,8032)

80C51(87C51,80C31)

80C52(87C52,80C32)

8044(8744,8344)

MSC-51单片机中央处理器

中央处理器是单片机内部的核心部件,它决定了单片机的主要功能特性。中央处理器主要由运算部件和控制部件组成。下面我们把中央处理器功能模块和有关的控制信号线联系起来加以讨论,并涉及相关的硬件设备(如振荡电路和时钟电路)。

1、运算部件:它包括算术、逻辑部件ALU、布尔处理器、累加器ACC、寄存器B、暂存器TMP1和TMP2、程序状态字寄存器PSW以及十进制调整电路等。运算部件的功能是实现数据的算术逻辑运算、位变址处理和数据传送操作。

MCS-51单片机的ALU功能十分强,它不仅可对8位变量进行逻辑“与”、“或”、“异或”、循环、求补、清零等基本操作,还可以进行加、减、乘、除等基本运算。为了乘除运算的需要,设置了B寄存器。在执行乘法运算指令时,用来存放其中一个乘数和乘积的高8位数;在执行除法运算指令时,B中存入除数及余数。MCS-51单片机的ALU还具有一般微机ALU,如Z80、MCS-48所不具备的功能,即布尔处理功能。单片机指令系统中的布尔指令集、存储器中的位地址空间与CPU中的位操作构成了片内的布尔功能系统,它可对位(bit)变量进行布尔处理,如置位、清零、求补、测试转移及逻辑“与”、“或”等操作。在实现位操作时,借用了程序状态标志器(PSW)中的进位标志Cy作为位操作的“累加器”.

运算部件中的累加器ACC是一个8位的累加器(ACC也可简写为A)。从功能上看,它与一般微机的累加器相比没有什么特别之处,但需要说明的是ACC的进位标志Cy就是布尔处理器进行位操作的一个累加器。

MCS-51单片机的程序状态PSW,是一个8位寄存器,它包含了程序的状态信息。

评论