集成PGIA、用于工业级信号的低功耗、多通道数据采集系统

AD7982 ADC噪声

本文引用地址:http://www.amcfsurvey.com/article/201610/311714.htmAD7982 ADC噪声与其固有量化噪声和内部元件(比如产生热噪声的无源元件)导致的噪声成函数关系。

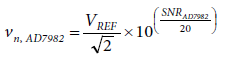

AD7982的rms输入电压噪声可以通过下式,利用其SNR额定值计算:

AD7982 (SNRAD7982)的SNR额定值约为96 dB(使用4.096 V基准电压源)。

AD7982输入端的单极点RC滤波器限制了来自上游元件的宽带噪声。较小的滤波器带宽可以通过进一步限制噪声功率而改善SNR:然而,其时间常数也必须足够短,以便建立电压反冲——这是因为AD7982输入端在采集阶段重新连接前端电路而发生电荷注入。适合系统的带宽至少为5 MHz(更多信息,请参见《模拟对话》文章:精密SAR模数转换器的前端放大器和RC滤波器设计)。

AD8475漏斗放大器噪声

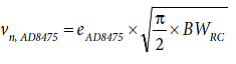

AD8475 (vn, AD8475)产生的rms噪声是其折合到输出NSD (eAD8475)以及AD7982输入端RC滤波器带宽(BWRC)的函数:

其中,eAD8475 = 10 nV/√Hz。

AD8251仪表放大器噪声

AD8251用作增益级,可通过将小幅度信号的幅度提升至更接近AD7982输入端的±VREF范围,从而改善它们的SNR。理想情况下,如果系统增益以系数G增加,则输入信号的SNR(单位:dB)将会改善:

然而,这种水平的改善实际上却是做不到的,因为宽带噪声同样为电路的噪声增益所放大。幸运的是,这种性能的下降不如信号增益导致的性能改善那么明显。

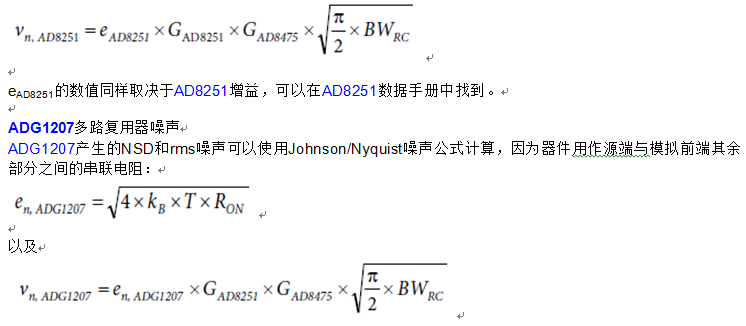

AD8251产生的rms噪声是其折合到输入NSD (eAD8251)、其增益设置(GAD8251)、AD8475的衰减系数(GAD8475)以及AD7982输入端的噪声滤波器带宽的函数。

各通道的电阻(RON)可在ADG1207数据手册中找到。

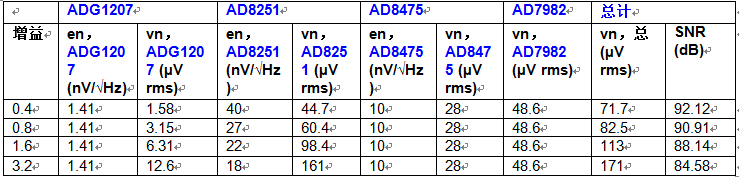

系统噪声性能的计算结果汇总如表2所示。总噪声的最大贡献因素是AD8251仪表放大器和AD7982 ADC。

表2.多通道数据采集系统的噪声性能

建立时间分析

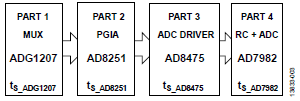

当图1中的电路对多通道进行采样时,每一个不同的输入都由ADG1207合并至一个时分多路复用信号。多路复用信号本质上是断续的,并且通常在较短的时间间隔内具有较大的电压阶跃。对于图1中的系统而言,两个连续通道之间的差分电压在ADG1207输入端可高达20 V,而分配的建立时间仅等于采样周期。

图3显示了图1中电路的建立时间模型。系统中每一个元件都有各自的建立特性(参见后文内容)。

图3.CN-0345电路建立时间模型

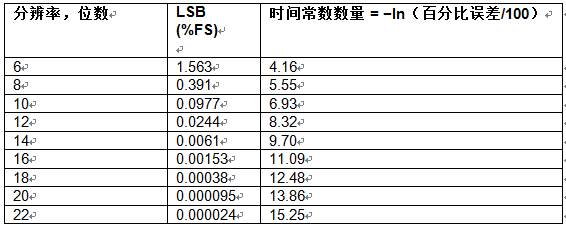

建立时间定义为模拟前端电路建立至某一精度的输入阶跃所需的时间。此精度单位通常采用百分比误差(比如0.1%或0.01%),但在转换系统中,将其与分辨率相关联也是非常有益的做法。例如,建立至16位分辨率大约等同于建立至0.001%。表3显示了单极点系统建立至百分比误差与建立至分辨率之间的关系。

表3.百分比误差和有效分辨率

估算含有多个元件的模拟前端建立时间并非易事,原因有多个。首先,很多器件都没有注明极高精度的建立时间特性。有源器件的建立时间与建立精度同样不是线性的,并且相比0.1%,建立至0.01%可能需要长达30倍时间。这有可能是因为放大器内部的长期热效应所导致。建立时间还与器件驱动的负载有关,并且通常不表征多个负载条件。

在没有特性测试平台的情况下测量高精度建立时间同样十分困难,因为存在示波器过驱和灵敏度的影响,此外生成具有足够上升时间和建立时间的输入脉冲也很困难。

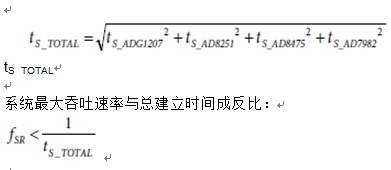

分析电路时,使用某些边界与假设,可以估算出建立时间。总建立时间可以通过单个元件建立时间的和方根(rss)计算:

ADG1207建立时间

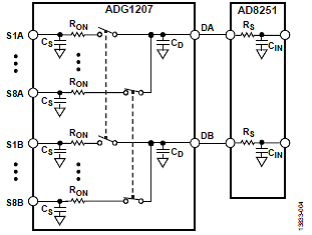

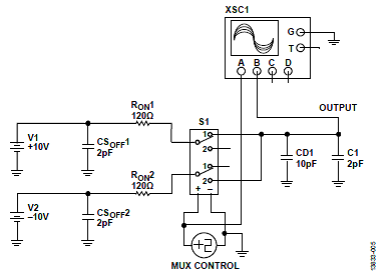

CMOS开关的等效电路可以近似看作理想开关与电阻(RON)串联连接,以及与两个电容(CS、CD)并联连接。随后,多路复用器级和相关的滤波器可以如图4所示建模。

图4.ADG1207建立时间模型

各通道工作情况类似于具有决定建立时间的相关时间常数的RC电路。动态切换通道使信号建立时间变得更复杂;通道完成切换后,上一次输出与当前输入的差异将会产生反冲瞬变。这种反冲类似于AD7982输入端发生的反冲,因为它进入了采集阶段。更多详细说明,请参见《模拟对话》文章:精密SAR模数转换器的前端放大器和RC滤波器设计。

图4中的电路使用NI Multisim™仿真,如图5所示,其中下列元件值来自相应的器件数据手册:

• RON = 120 Ω

• CS = 2 pF

• CD = 10 pF

• RIN||CIN = 1.25 GΩ||2 pF

AD8251的输入电阻(RIN)足够大(1.25 GΩ),仿真时可以省略。

图5.ADG1207的Multisim™建立时间模型

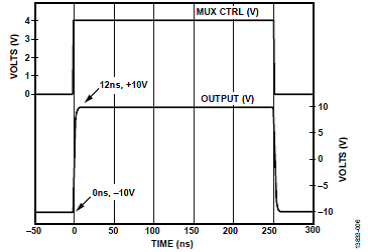

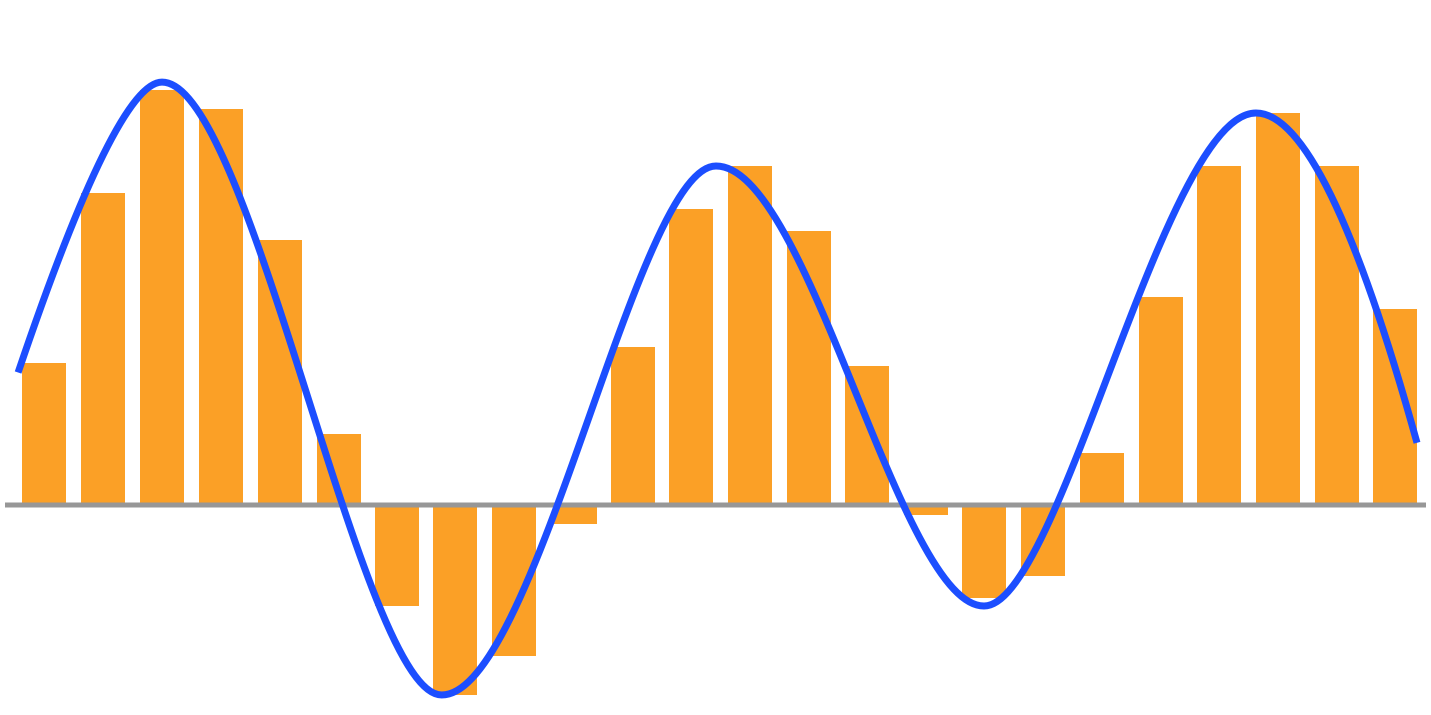

仿真结果如图6所示。ADG1207输出建立至10 V的0.001%所需的时间等于tS_ADG1207 = 12 ns。

图6.ADG1207仿真模型的建立时间波形

AD8251和AD8475的建立时间

AD8251数据手册给出了各种增益配置下,各输入电压步长情况下低至0.001%误差的建立时间。给定10 kΩ负载和1增益设置,则AD8251输出端能够在1 μs内,以20 V阶跃建立至0.001%。1增益设置所需的建立时间最长,因此建立时间分析将使用1 µs。

然而,当AD8251驱动AD8475的其中一个输入时,其输入阻抗为2.92 kΩ而不是10 kΩ,因此1 µs这个数字可能并不准确。另外也无法保证AD8251建立至18位分辨率的建立时间,因为建立时间与精度之间的关系是非线性的。因此,估计建立时间最好使用0.001%误差(或16位分辨率)。

AD8475建立至0.001%的建立时间额定值为50 ns(2 V差分输出阶跃)。AD8475输出端上的预计最大电压步长为基准电压(VREF)的两倍,或者大约等于8 V。假定建立时间与输出电压阶跃成正比,则对于8 V阶跃来说,0.001%(16位)建立时间约为200 ns (4 × 50 ns)。

因此,各放大器的建立时间为:

• tS_AD8251 = 1 µs

• tS_AD8475 = 200 ns

RC噪声滤波器建立时间和AD7982

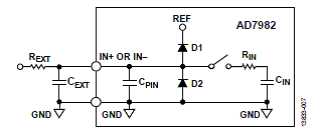

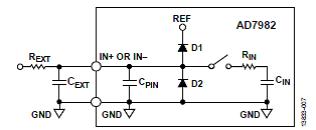

图7显示了AD7982输入等效电路。REXT和CEXT是ADC之前RC宽带噪声滤波器中的元件。RIN和CIN分别是AD7982的输入电阻和电容。CIN主要是内部容性数模转换器(DAC)。CPIN主要是引脚电容,可忽略。这些元件值如下:

• REXT = 10 Ω

• CEXT = 1200 pF

• RIN = 400 Ω

• CIN = 30 pF

图7.AD7982和RC噪声滤波器建立时间模型

AD7982采用内部容性DAC和电荷再分配算法确定其输出码。转换过程包含两个阶段——采集和转换。在采集阶段,容性DAC连接AD7982的输入端子。在转换阶段,它断开与输入端子的连接,内部逻辑执行电荷再分配算法。转换阶段的最大额定时间为710 ns。

信号必须在采集阶段结束前完成建立,以便进行精确转换。为了最大化信号建立的时间,多路复用器会在AD7982开始转换阶段时立即切换通道。

除了从AD8475输出端的多路复用信号建立外,RC噪声滤波器和AD7982输入还必须建立至采集阶段开始时出现的电压反冲。请参见《模拟对话》文章:精密SAR模数转换器的前端放大器和RC滤波器设计。

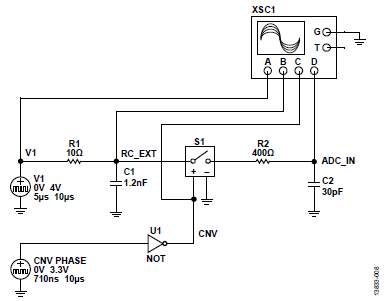

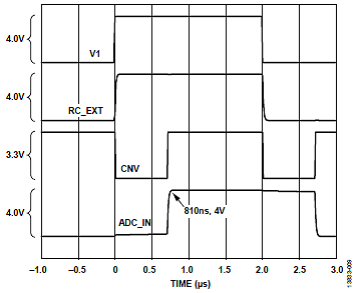

图7中电路的建立时间采用NI Multisim™进行仿真,如图8所示。V1表示AD7982各输入端的预期最大电压阶跃(来自AD8475的单端输出)。CNV和S1仿真AD7982从转换阶段(V1改变数值时发生)到采集阶段(转换开始后710 ns)的切换。CNV保持S1开路,直到V1从0 V阶跃至4 V之后的710 ns,表示转换阶段到采集阶段的切换。ADC_IN表示AD7982在CNV上升沿的采样电压。

系统这部分的建立时间等于V1切换到4 V(时间 = 0时)与ADC_IN建立至4 V的0.001%之间的时间。

图8.AD7982和RC噪声滤波器的Multisim™建立时间模型

仿真结果如图9所示。输出建立至4 V的0.001%所需时间为tS_AD7982 = 810 ns。

图9.AD7982和RC噪声滤波器仿真模型的建立时间波形

总系统建立时间

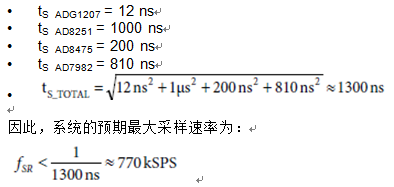

图1中整个电路的总建立时间现在可以通过计算各元件建立时间的rss值得到:

评论