锁相环在微机保护中的应用

摘要:针对微机保护中采用传统的采样方法,采样频率难以自动跟踪被测量的频率变化而发生变化,必然会导致FFT运算产生误差。本文采用锁相环 同步采样技术实现对微机保护装置中交流电压、电流信号的频率和相位进行锁定,以提高测量精度和实时性。结合锁相环

同步采样技术实现对微机保护装置中交流电压、电流信号的频率和相位进行锁定,以提高测量精度和实时性。结合锁相环 控制AD7656模数转换芯片的实验,证明整周期同步采样在微机保护装置中的可行性,解决了软件同步采样的实时性差、软件编写复杂等问题。

控制AD7656模数转换芯片的实验,证明整周期同步采样在微机保护装置中的可行性,解决了软件同步采样的实时性差、软件编写复杂等问题。

微机保护装置广泛地应用于电力系统中,担负着保护电力系统的重要任务,在配电网中还起着测控的作用,如何准确、实时的测量电压、电流量直接关系到微机保护装置的性能。由于电网的频率是变化的,并且微机保护装置是工作在故障状态,N点等间隔采样并不能恰好使每一点处在一个整周期内,势必造成测量的误差。采用传统的方法,采样频率难以自动跟踪被测量的频率变化而变化,必然会导致FFT运算产生误差。这种误差来源于非整周期采样引入的窗截断,这样FFT就不能算出各次谐波分量的准确值。因此,本文提出采用锁相环 同步采样技术实现对微机保护装置中交流电压、电流信号的频率和相位进行锁定,以提高测量精度和实时性。

同步采样技术实现对微机保护装置中交流电压、电流信号的频率和相位进行锁定,以提高测量精度和实时性。

1 同步采样的分类

减少和消除同步误差的方法是采用同步采样技术,同步采样使每个采样点均匀的分布在一个整周期内。同步采样可以利用软件实现,也可以利用硬件实现。软件实现同步采样,是利用比较器将交流信号变成方波信号,CPU检测两次上升沿或两次下降沿之间的时间间隔,即一个周期的时间,然后根据采样点数计算出采样间隔,通过软件控制AD采样。虽然利用软件实现同步采样,可以减少硬件的复杂程度,但是增加了CPU的负担和软件编写的难度,降低了微机保护装置的实时性,同时电网的频率是波动的,相邻两个周期的频率有差别,也会引起误差。用硬件实现同步采样,硬件相对复杂,直接控制AD,但是减少了CPU的开销和软件编写的难度,同时从根本上消除因采样不同步而造成的误差。

2 锁相环 的工作原理

的工作原理

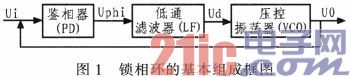

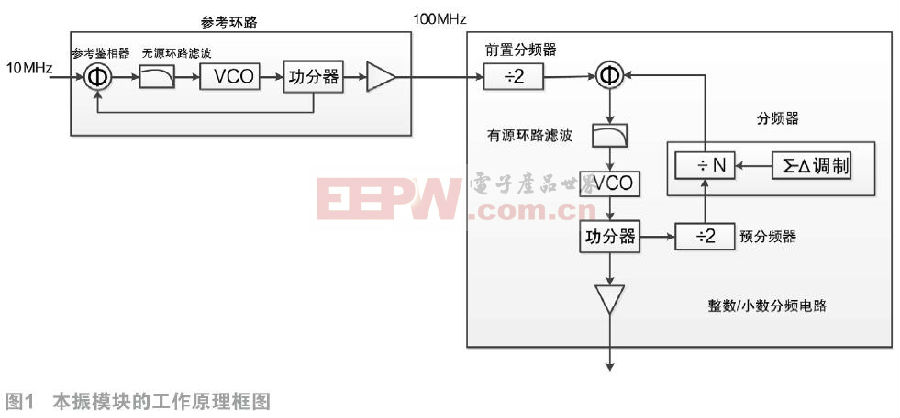

锁相环 的基本组成框图如图1,它主要由鉴相器(PD)、低通滤波器(LF)和压控振荡器(VCO)组成。

的基本组成框图如图1,它主要由鉴相器(PD)、低通滤波器(LF)和压控振荡器(VCO)组成。

压控振荡器的输出U0反馈至鉴相器的输入端,其输出频率的高低由低通滤波器上的平均电压Ud的大小决定。外部输入信号Ui与来自压控振荡器的反馈信号U0相比较,产生的误差输出电压Uphi正比于Ui和U0两个信号的相位差,经过低通滤波器滤除高频分量后,得到平均电压Ud。平均值电压Ud朝着减小U0和Ui之差的方向变化,直到压控振荡器输出频率和输入信号频率一致。这时两个信号的频率相同,两相位差保持恒定即相位锁定。当锁相环入锁时,在一定范围内具有“捕捉”信号的能力,压控振荡器自动跟踪输入信号的变化。

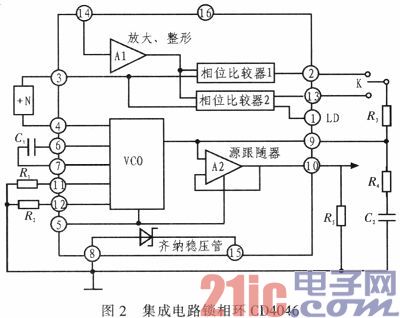

本文使用的是集成电路锁相环CD4046,其内部结构如图2所示。主要由相位比较器I和Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。相位比较器I采用异或门,即两个输入端信号的电平相异时,输出端信号(管脚2)Uphi为高电平;反之,输出为低电平。当两个输入信的相位差在0°-180°范围内变化时,Uphi的脉冲宽度也随之改变。相位比较器Ⅱ对输入信号占空比的要求低,允许输入非对称信号,具有很宽的频率捕捉范围,而且不会锁定输入信号的谐波。相位比较器Ⅱ提供数字误差信号和锁定信号两种输出,进入锁定状态时,两个输入信号之间保持0°相移。

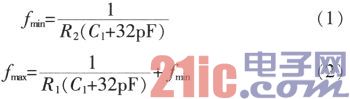

集成电路锁相环CD4046采用的是RC型压控振荡器,需要使用外接电阻R1和电容C1作为充放电元件。当锁相环对输入的跟踪信号的频率宽度有要求时,还需要外接电阻R2。压控振荡器VCO的振荡频率取决于外接电阻R1、R2、电容C1及压控振荡器的控制端(管脚9)。根据公式(1)和(2)可以计算出压控振荡器的大致工作范围,外接电阻、电容可参考在以下范围内:当VDD大于或等于5V时,C1大于等100pF;R1、R2、R3大于等于5 kΩ,小于等于1 MΩ,具体的电阻、电容值还需要通过试验来确定。

3 锁相环与AD7656采样电路的设计

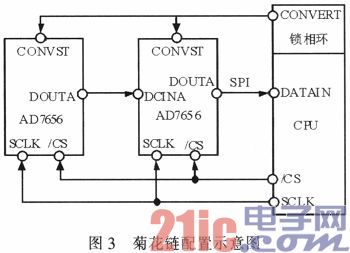

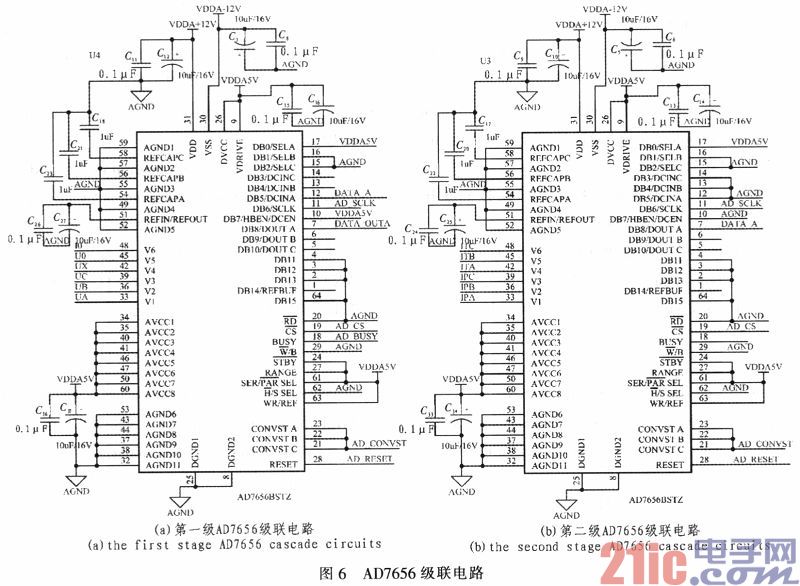

本装置需要采集12路模拟信号,包括:3路保护/测量用电压,1路零序电压、1路线路抽取电压、3路保护用电流、3路测量用电流和1路零序电流。一块AD7656只能同时采集6路模拟信号,因此,需要2块AD7656。同时CPU的引脚有限,为了减少占用CPU的资源,采用串行方式SPI读取AD7656中的数据,多块AD7656可以采用菊花链的方式级联在一起。如图3所示,两块AD7656之间通过一路SPI级联,CPU从DOUTA管脚读取采样后的数据;锁相环控制AD的CONVST管脚启动采样;CS为片选信号,低电平有效,可以直接接地,使AD一直处于选中状态:SCLK是CPU为AD提供的时钟信号。

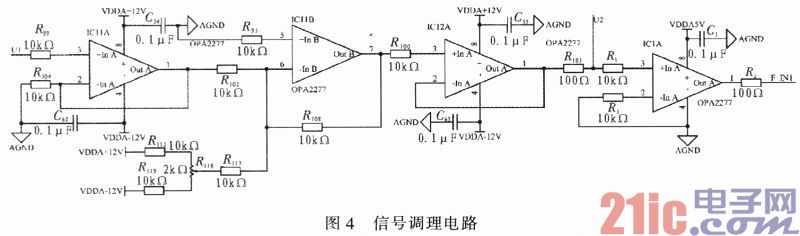

3.1 信号调理电路

如图4所示,第一级运算放大器构成了电压跟随器,减小输出电阻,提高带负载能力;第二级运算放大器构成了反向加法电路,用于调零漂;第三级运算放大器也构成了电压跟随器,减小输出电阻,即减小AD内部的时间常数,提搞AD的采样频率。同时,U2还经过电压比较器和地电位比较后,输出方波F_IN1,作为锁相环的输入。

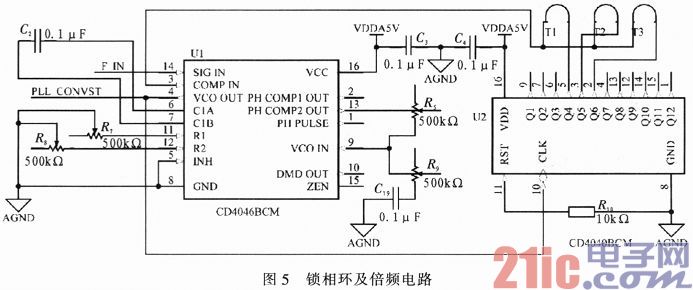

3.2 锁相环及倍频电路

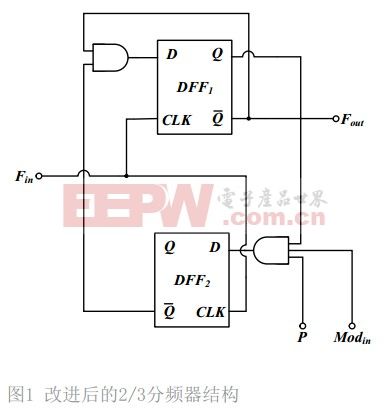

如图5所示,分频器选用CD4040,设计时通过跳线T1、T2、T3设置了3个可选的分频倍数,分别为16倍频、32倍频、64倍频。图4(b)的输出信号接入CD4046的14管脚,作为输入信号,4管脚是输出信号,去控制AD7656启动采样。

3.3 AD7656采样电路

如图6所示为AD7656级联电路图,锁相环的输出信号PLL-CONVST控制两块AD7656的21、22、23管脚,同时启动12路采集;CPU作为主机为AD7656的11管脚(AD—SCLK)提供时钟信号。CPU从图6(a)的管脚7(DATA—OUTA)通过SPI读取数据;图6(a)的12管脚与图6(b)的管脚7连接,实现两块AD7656的级联;通过判断AD7656的18管脚(AD—BUSY)来提醒CPU读取转换数据。

4 实验结果

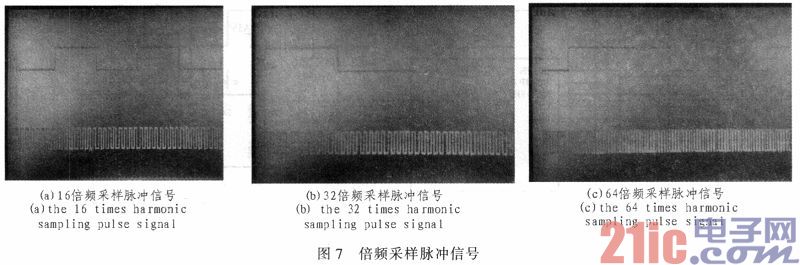

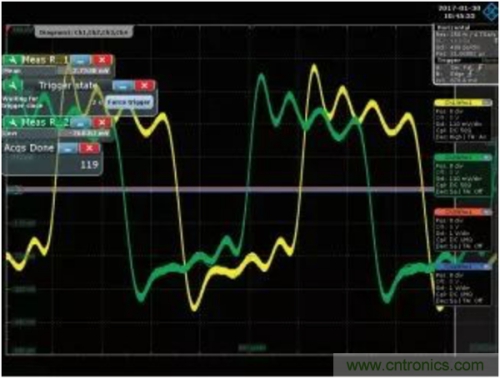

如图7(a)-(c)所示为倍频采样脉冲信号,上半屏为工频50 Hz的方波信号,下半屏为倍频后的采样脉冲信号。图7(a)为16倍频采样脉冲信号,图7(b)为32倍频采样脉冲信号,图7(c)为64倍频采样脉冲信号。从图中可以发现,利用锁相环CD4046和分频器CD4040实现了硬件同步采样。同时,采样脉冲的波形在上升沿后有一个下降的过程,由于AD7656是上升沿触发采样,因此并不影响AD7656启动采样。

5 结束语

基于锁相环的同步采样技术,解决了软件同步采样的实时性差、软件编写复杂等问题。在微机保护装置中,实现了等周期同步采样,提高了交流电流、电压参数的测量精度和时实性。此外,该方法还可以应用于其他交流采样算法,比如电能质量监测、故障录波等,具有实用价值。

评论