基于SOC的星载微型GNSS接收机设计

摘要:针对皮纳型卫星对星载GNSS接收机小型化、低功耗以及低成本的要求,提出采用片上系统(SoC)技术完成星载微型GNSS接收机的设计。在该设计中,基带信号的捕获、跟踪与定位解算等全部在SoC内完成,具有集成度高与系统灵活性高等优势。将设计的原理样机与国外几款星载微型GNSS接收机性能参数进行对比,结果表明,该星载微型GNSS接收机原理样机重约45 g,尺寸100x60×10 mm,功耗约3 W,兼容处理GPS L1/L2、BDS B1/B2信号能力,可完成双模单频、单模双频、双模双频等多种模式的灵活配置,综合性能要优于现有的几款星载微型GNSS接收机。

本文引用地址:http://www.amcfsurvey.com/article/201610/308269.htm近年来,皮纳型卫星凭借其发射灵活、成本低、功能密度高、研制周期短等一系列优势,成为当前国际空间技术研究的热点。由于皮纳型卫星平台空间有限,全球导航卫星系统(GNSS)接收机往往成为皮纳型卫星唯一的测控手段。但是受限于皮纳型卫星平台空间有限、功率有限、成本有限等条件,相对于传统星载GNSS接收机,对皮纳型卫星的星载GNSS接收机提出小型化、低功耗、低成本等更高的要求。

商用现货(COTS)器件具有高集成、高密度、功耗低、价格低、易于采购、设计灵活、性能好等优点。此外SoC技术的发展,使得由多个分立器件实现的功能集成到单芯片,具有功耗低、集成度高、系统灵活性高等优势。因此把先进的商用SoC技术应用于星载GNSS接收机,能很好满足皮纳型卫星对星载GNSS接收机的应用需求。

在目前国外皮纳型卫星GNSS接收机设计中,SGR-05U接收机与Plaoenix GPS接收机均采用GP4020基带处理芯片,仅包含12个GPS L1 C/A码相关器通道,处理能力不足,FOTON双频GPS接收机也仅能处理L1 C/A和L2C信号,采用TI C6457数字信号处理器,功耗偏高约4.5 W。当前基于COTS器件的GNSS接收机在国外皮纳型卫星中已经得到了较为普遍的应用,多采用成熟的GP4020基带处理芯片或处理器与FPGA架构,但在国内,采用COTS器件来设计星载微型GNSS接收机还处于起步阶段。因此,有必要开发出一款采用商用SoC技术兼容BDS/GPS信号的星载微型GNSS接收机,提高接收机集成度与灵活性并降低接收机功耗以及成本,从而满足皮纳型卫星对微型GNSS接收机空间应用提出的要求。

文中对采用SoC的星载微型GNSS接收机系统设计进行介绍,包括接收机系统架构以及采用SoC的软硬件协同设计方法,将设计的原理样机与国外几款星载微型GNSS接收机性能参数进行对比,验证了本文提出的采用SoC技术设计的星载微型GNSS接收机的优越性。

1 星载微型GNSS接收机系统设计

1.1 系统架构

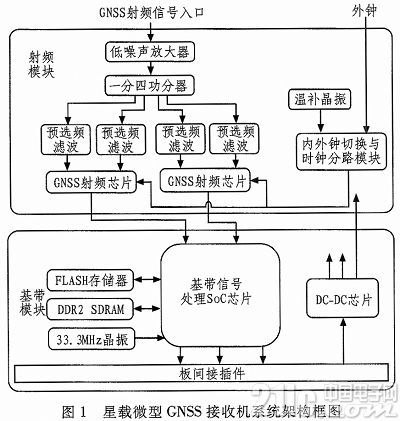

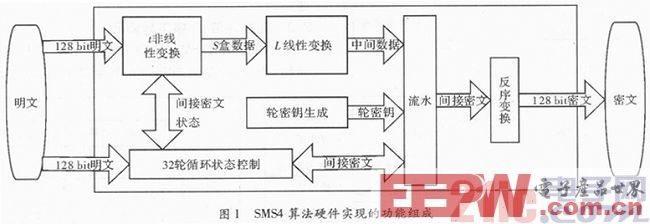

星载微型GNSS接收机采用全COTS器件方案,接收机为单板结构,主要由射频模块与基带信号处理模块两部分组成,如图1所示。其中,射频模块完成GNSS信号的放大、滤波、下变频及AD采样处理,并将获得的数字中频信号提供给基带信号处理模块。射频模块时钟电路主要为GNSS射频芯片提供基准时钟,可以完成内外钟切换。基带信号处理模块完成捕获、跟踪、位同步、帧同步及定位解算等一系列处理,最后将定位结果发送给数管单元。基带模块同时实现DC/DC电源转换,为射频模块、基带模块供电。

基带信号的捕获、跟踪与定位解算等全部在SoC内完成,具有集成度高与系统灵活性高等优势,整个系统设计中最关键的部分就是SoC软硬件协同设计。

1.2 SoC的软硬件协同设计

SoC内包含ARM硬核处理器、可编程逻辑以及多种外设IO资源,处理器与可编程逻辑部分、外设IO接口通过片上AXl4总线进行通信,集成处理器和可编程逻辑的系统架构提供了传统的双芯片(外部处理器与FPGA配合)无法提供的IO带宽、处理效率和功耗估算。SoC具有高性能、灵活的可配置性能、小型化低功耗特性等优势,用于星载微型GNSS接收机能很好满足皮纳型卫星的应用需求。

软硬件协同设计技术采用并行设计和协同设计的思想,设计效率大大提高,可大幅缩短星载微型GNSS接收机开发周期,完成接收机的批产,符合快速响应、快速组装、快速发射需求。

1.2.1 SoC硬件设计

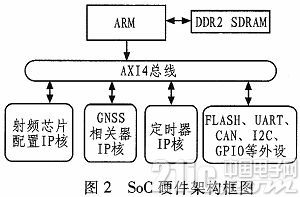

图2给出了整个SoC硬件架构。ARM处理器作为SoC的核心功能单元,负责SoC片上AXI4总线上的UART、CAN、I2C、GPIO、FPGA等外设资源的配置与通信,并承担导航信息处理任务。射频芯片配置代码以及相关器代码均被封装为IP核,ARM处理器通过射频芯片配置IP核对射频芯片的工作模式进行配置,使其工作在GPS L1/L2、BDS B1/B2工作模式。累加数据获取中断信号采用AXI Timer IP核在ARM处理器的控制下产生,AXI Timer IP核的时钟由总线钟提供。GPS/BDS导航信息处理相关器代码也被封装为IP核,挂接在AXI4总线上。

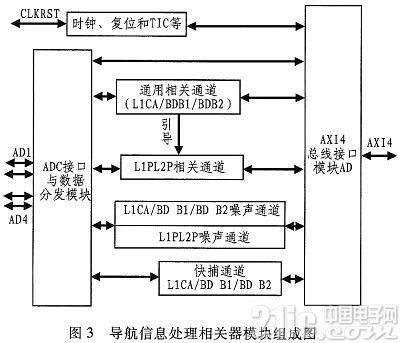

GPS/BD2导航信息处理相关器,主要完成GPS L1/L2、BD2 B1/B2信号的载波剥离、码剥离和相关累加,并送给处理器完成信号的捕获跟踪环路处理。导航信息处理相关器主要由快速捕获模块、通用相关通道模块、L1PL2P相关通道模块和噪声通道模块组成,各个模块之间流程如图3所示。

在SoC硬件环境的构建中,累加数据获取中断直接采用了定时器IP核,在处理器的控制下完成计时,周期性的产生中断信号,完成累加量的及时获取。射频芯片配置模块也被封装成用户IP核,在初始化阶段完成射频芯片的配置,分别配置成GPS L1/L2、BD2 B1/B2通道。经验证,自定义射频芯片配置模块可以直接复用,有效减少设计复杂度,提高了设计效率。

硬件环境构建完成后,即可在EDK XPS(Xilinx Platform Studio)中生成网表、比特流文件。

1.2.2 SoC导航信息处理软件设计

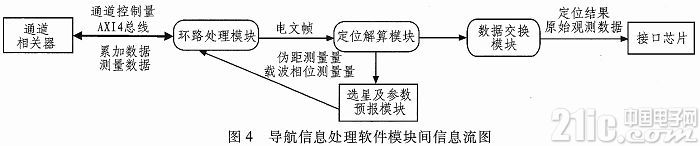

导航信息处理软件通过控制数字通道相关器,对其产生的通道累加数据和通道测量数据进行处理,完成GPS和BDS导航信号的捕获跟踪、定位解算,可提供每秒一次的用户时间、位置、速度,并通过接口输出给数管分系统。导航信息处理软件模块主要分为环路处理模块、定位解算模块、选星及参数预报模块及数据交换模块。图4给出了星载微型GNSS接收机导航信息处理软件模块间信息流图。

环路处理模块完成导航星信号初始捕获后,实现信号的精确跟踪与同步,并对信号解调转为原始电文帧。具体需完成的操作包括:码精确跟踪、载波精确跟踪、比特位同步、电文帧同步。

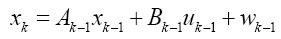

定位解算模块的功能是通过环路处理模块提供的载波相位、码相位、载波周数、传输延时、导航卫星历书及其时间标记等信息的处理,得到伪距、伪距变化率、导航卫星时钟及导航卫星历书、卫星星历等测量信息,用这些测量数据进行导航定位求解,以确定出用户当前运动状态(包括三维位置坐标、三维速度坐标分量等)和时间信息。

选星及参数预报模块的功能是为通道提供搜捕依据,即预报可以捕获的导航卫星及对应的多普勒频移。

数据交换模块的功能是按照数据通信协议将定位结果和原始观测数据输出给数管分系统。

完成导航信息处理软件代码的编写,在EDK SDK(Software Development Kit)中生成二进制可执行文件后,即可进行软硬件协同设计,在SDK中与生成的硬件平台文件、板级支持包文件以及bit文件进行协同调试,调试通过后,即可生成.mcs文件,并烧录到flash中。

2 原理样机

图5给出了采用SoC技术实现的星载微型GNSS接收机原理样机图(与市面某款智能手机对比图),接收机尺寸大小为100x60x10 mm,重量约45 g,功耗约为3 W,兼容处理GPS L1/L2、BDS B1/B2信号,符合皮纳型卫星对接收机提出的应用需求。

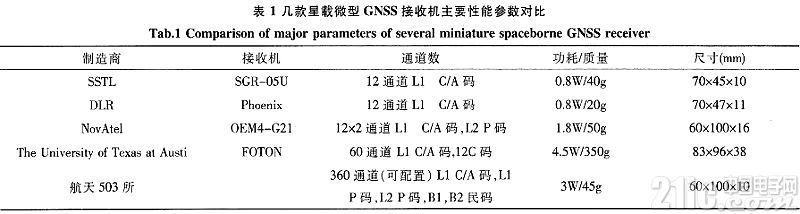

表1给出了采用SoC技术实现的星载微型GNSS接收机与几款国外微型GNSS接收机主要性能对比。由表中结果可知,采用SoC技术实现的微型GNSS接收机尺寸与OEM4-G2L接收机相当,比其余三款接收机尺寸稍大;质量与SGR-05U接收机和OEM4-G2L接收机相当,比Phoenix接收机略大,但远小于FOTON接收机;功耗比FOTON接收机小,比其余三款接收机大;通道数比FOTON接收机少,但是比其余三款接收机多,SGR-05U接收机与Phoenix接收机只能处理L1C/A码,OEM4-G2L接收机能处理L1C/A码与L2 P码,FOTON接收机能处理L1 C/A码与L2C码,采用SoC技术实现的星载微型GNSS接收机能处理L1 C/A码、L1 P码、L2 P码、B1民码与B2民码,处理能力更强,更为灵活。由此可见,采用SoC技术实现的星载微型GNSS接收机综合性能要优于现有的其余几款星载微型GNSS接收机。

3 结束语

本文针对皮纳型卫星的应用需求,设计了一种采用SoC技术实现的星载微型GNSS接收机。该星载微型GNSS接收机具有质量小、尺寸小及成本低的特点,兼容处理GPS L1/ L2、BDS B1/B2信号,可完成双模单频、单模双频、双模双频等多种模式的配置,能为皮纳型卫星等空间飞行器提供精确的定位与授时服务。

评论