时钟发生器性能对数据转换器的影响

摘要

本文引用地址:http://www.amcfsurvey.com/article/201610/307855.htm数据转换器是通信系统中的重要元件,构成模拟传输媒介(如光纤、微波、射频和FPGA及DSP等数字处理模块)之间的桥梁。系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。本文将详细讨论时钟发生器、相位噪声和抖动对数据转换器(ADC和DAC)的动态范围和线性度的影响。文中将就时钟抖动对转换器SNR的影响进行理论分析,同时介绍运用ADI高性能时钟发生器得到的仿真结果。

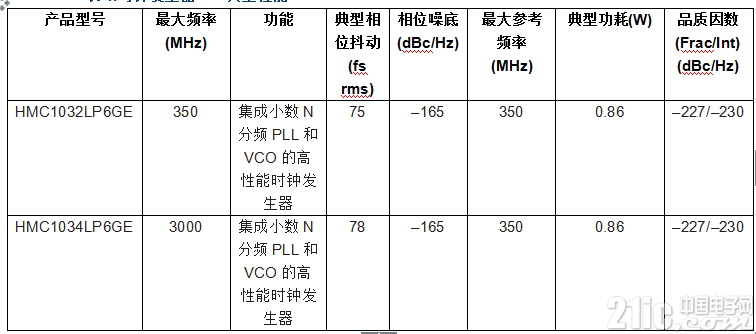

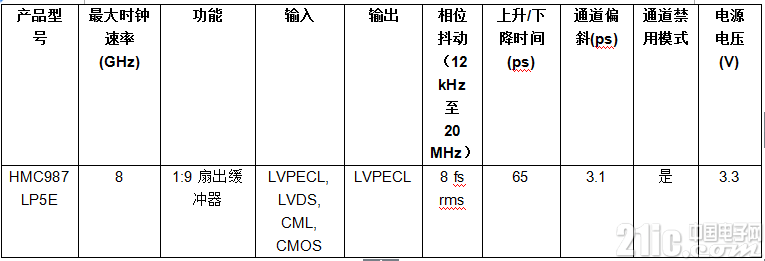

ADI开发了一个独特的高性能时钟分配和时钟发生产品系统,使系统设计师可以实现数据转换器的最佳性能。HMC1032LP6GE和HMC1034LP6GE为SMT封装时钟发生器,是多种高性能蜂窝/4G基础设施、光纤和网络应用的理想选择,在同类产品中具有最佳的抖动性能和行业领先的相位噪底。HMC987LP5E 1:9扇出缓冲器是关键应用中充当时钟驱动器的最佳选择,噪底超低,仅−166 dBc/Hz。这些器件的主要技术规格如表1和表2所示。

系统考虑因素

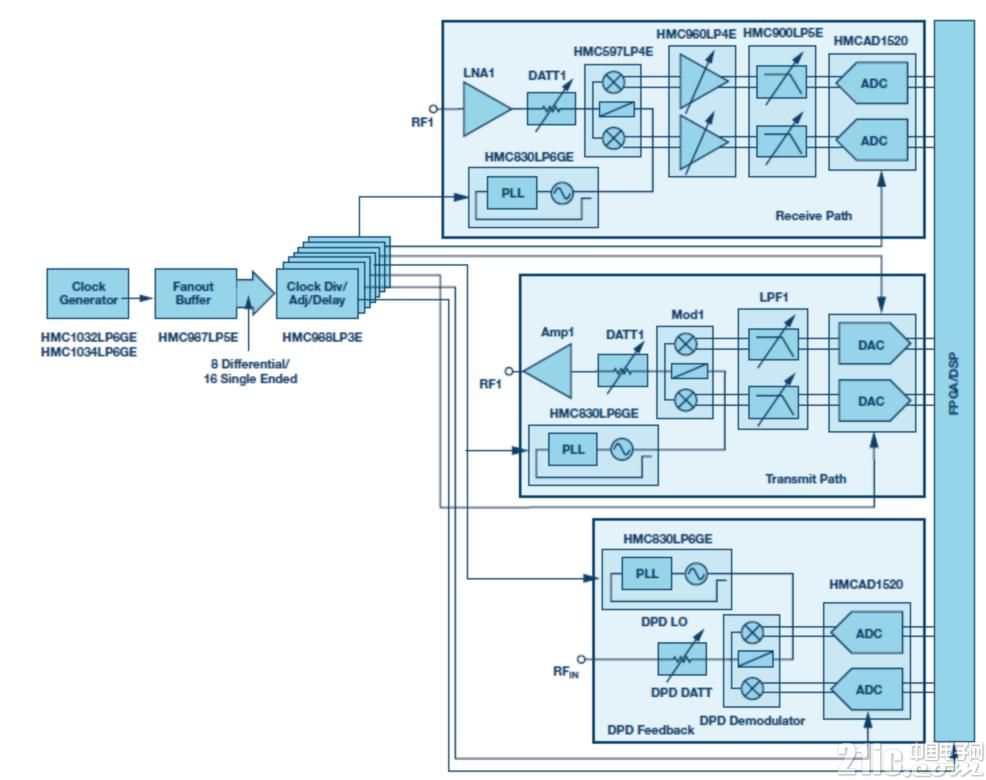

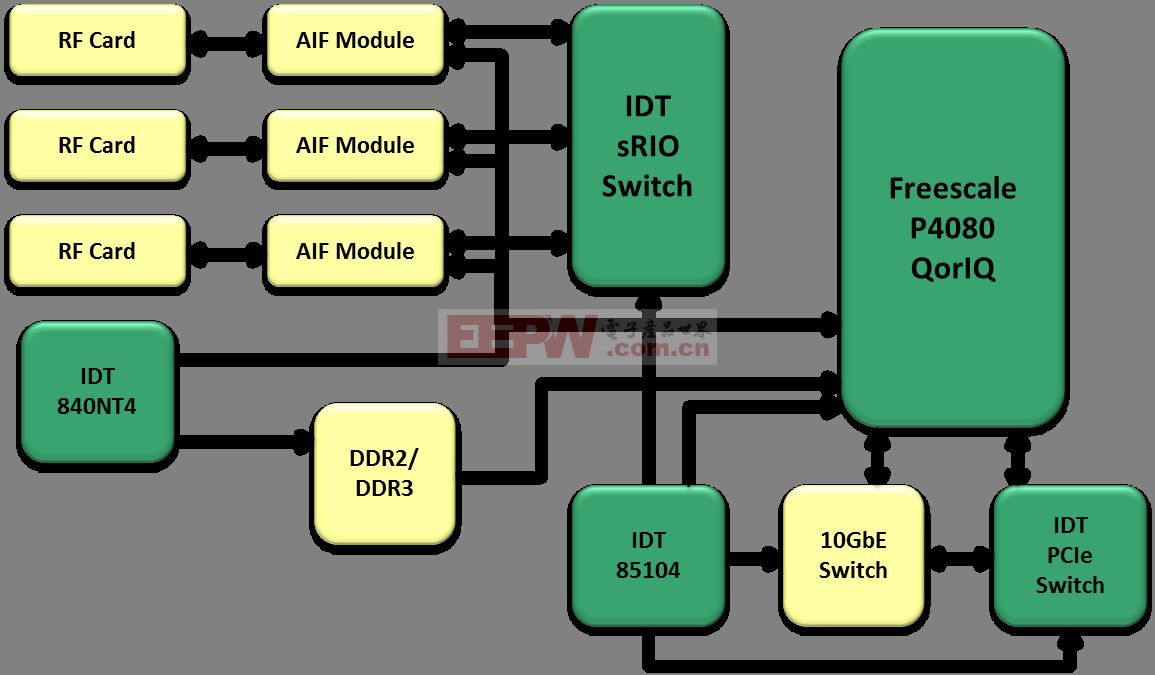

采用MIMO(多输入多输出)架构的典型LTE(长期演进)基站如图1所示。该架构由多个发射器、接收器和DPD(数字预失真)反馈路径构成。各种发射器/接收器组件(如数据转换器(ADC/DAC))和本振(LO)要求采用低抖动参考时钟以提高性能。其他基带组件也要求各种频率的时钟源。

表1.时钟发生器——典型性能

表2.时钟分配产品——典型性能

2 时钟发生器性能对数据转换器的影响

图1.面向采用MIMO架构的典型LTE基站的时钟时序解决方案。

用于实现基站间同步的时钟源一般来自GPS(全球定位系统)或CPRI(通用公共射频接口)链路。这种源一般拥有优秀的长期频率稳定性;但它要求把频率转换成所需的局部参考频率,以实现良好的短期稳定性或抖动。高性能时钟发生器(如HMC1032LP6GE)可执行频率转换操作并提供低抖动时钟信号,在此基础上,这些信号可能会分配给各种基站组件。选择最佳时钟发生器至关重要,因为欠佳参考时钟会增高LO相位噪声,结果会提高发射/接收EVM(误差矢量幅度)和系统SNR(信噪比)。高时钟抖动和噪底也会影响数据转换器,因为它会降低系统SNR并导致数据转换器杂散辐射,从而进一步降低数据转换器的SFDR(无杂散动态范围)。结果,低性能时钟源最终会降低系统容量和吞吐量。

时钟发生器技术规格

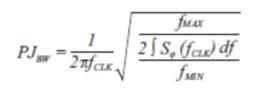

尽管关于时钟抖动的定义多种多样,但在数据转换器应用中,最合适的定义是相位抖动,其单位为时域ps rms或fs rms。相位抖动(PJBW)是通过时钟信号相位噪声在载波特定失调范围内的积分推导出来的抖动,计算公式如下:

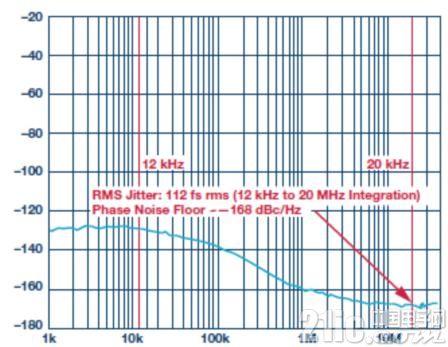

fCLK为工作频率;fMIN/fMAX表示目标带宽,S(fCLK)表示SSB相位噪声。积分带宽的上限和下限(fMIN/fMAX)因具体应用而异,取决于设计敏感的相关频谱成分。设计师的目标是选择所需带宽中的积分噪声最低或者相位抖动最低的时钟发生器。传统上,时钟发生器的特性是在12 kHz至20 MHz积分条件下测得的,这也是光学通信接口(如SONET)的指定要求。虽然这可能适用于一些数据转换器应用,但要捕获高速数据转换器采样时钟的相关噪声曲线,通常需要更宽的积分频谱,具体是指20 MHz以上。在测量相位噪声时,噪声远远偏离载波频率。例如,数据转换器采样实际使用的时钟频率一般称为远远偏离载波相位噪声。该噪声的限值通常称为相位噪底,如图2所示。该图所示为ADI HMC1032LP6GE时钟发生器的实际测量图。相位噪底在数据转换器应用中显得格外重要,其原因在于转换器SNR对其时钟输入端的宽带噪声极其敏感。当设计师评估时钟发生器选项时,必须把相位噪底性能作为一项关键基准指标。

图2.HMC1032LP6GE的相位噪声和抖动性能。

在图2中,工作频率为~160 MHz时,积分相位抖动为~112 fs rms,积分带宽为12 kHz至20 MHz,相位噪底为~–168 dBc/Hz。这里值得注意的是,在为数据转换器选择最合适的时钟发生器时,设计师不仅要参考频域的相位噪声测量值,同时也要参考时域的时钟信号质量测量值,比如占空比、上升/下降时间。

数据转换器的性能

为了描述时钟噪声对数据转换器性能的影响,不妨将转换器视为一个数字混频器,二者仅存在一个细微差异。在混频器中,LO的相位噪声将添加到被混频的信号中。在数据转换器中,时钟的相位噪声将叠加到转换输出中,但受信号与时钟频率之比的抑制。时钟抖动会导致采样时间错误,表现为SNR下降。

时间抖动(T抖动)即是采样时间中的rms误差,单位为秒。

在有些应用中,可能会利用时钟抖动来减少时钟信号的抖动,但这种方法存在显著的缺陷:

Ø 滤波器虽然可能会消除时钟信号的宽带噪声,但窄带噪声却保持不变。.

Ø 滤波器的输出通常是一个类似于正弦波的慢压摆率,会影响时钟信号对时钟路径内部噪声的敏感度。

Ø 滤波器消除了灵活性,无法更改时钟频率以实施多个采样速率架构。

一种更实际的办法是用一个拥有快压摆率和高输出驱动能力的低噪声时钟驱动器来最大化时钟信号的斜率。这种方法可以优化性能,原因如下:

Ø 消除时钟滤波器之后可以降低设计的复杂性,减少组件数量。

Ø 快速上升时间会抑制ADC时钟路径内部的噪声。

Ø 窄带和宽带噪声都可以通过选择最佳时钟源来优化。

Ø 可编程时钟发生器可实现不同的采样速率,因而可以增加解决方案对不同应用的适应能力。

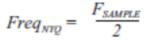

超低时钟噪底至关重要。远远偏离载波的时钟抖动噪声在ADC中采样,并叠加进ADC数字输出频段中。该频段受奈奎斯特频率限制,后者定义为:

时钟抖动通常由ADC时钟信号的宽带白噪底所主导。虽然ADC的SNR性能取决于多种因素,但时钟信号宽带抖动的影响由下式决定:

如上式所示,与混频器不同,时钟抖动的SNR贡献与ADC模拟输入频率(fIN)成正比。

在驱动ADC时,时钟噪声受时钟驱动器路径中的带宽限制,一般由ADC时钟输入电容主导。宽带时钟噪声会调制较大的输入信号并叠加进ADC输出频谱中。时钟路径的相位噪声会降低输出SNR性能,降幅与输入信号的幅度和频率成比例。最差情况是,在存在小信号的情况下还存在较大的高频信号。

在现代无线电通信系统中,情况经常是,输入端存在多个载波信号,然后在DSP中对各目标信号进行过滤,以匹配信号带宽。在许多情况下,处于一个频率的较大的无用信号会与时钟噪声混合,结果会降低ADC通带中其他频率下的可用SNR。在这种情况下,目标SNR为所需信号带宽中的SNR。另外,上面的SNRJITTER值实际上是相对于最大信号(通常是一个无用信号或阻塞信号)的幅度的。

所需目标信号频段中的输出噪声取决于:

a. 在给定输入频率下,计算时钟噪声和较大无用信号条件下ADC性能的降幅;例如,计算ADC全带宽中的SNR。

b. 用所需信号带宽与数据转换器全带宽之比计算所需信号带宽中的SNR。

c. 基于无用信号在满量程以下的幅度增大该值。

步骤b的结果只是为了按以下方式修正前面所示的SNR等式:

Ø SNRJITTER:在存在频率为fin的大信号且采样速率为fs的条件下,时钟抖动在带宽fBW中的SNR贡献。

Ø fIN:满量程无用信号的输入频率,单位为Hz。

Ø TJITTER:ADC时钟的输入抖动,单位为秒。

Ø fBW:所需输出信号的带宽,单位为Hz。

Ø fs:数据转换器的采样速率,单位为Hz。

Ø SNRDC:数据转换器在直流输入条件下的SNR,单位为dB。

最后,在存在满量程阻塞信号的条件下,目标信号频段中的最大可用SNR只是抖动与直流贡献噪声功率之和。

例如,对于ENOB为12.5位(直流)或者SNR为75 dB的500 MSPS数据转换器,则在相当于采样速率一半的带宽中在250 MHz的频率下进行评估。如果目标信号的带宽为5 MHz,则在接近直流时的可能SNR(带宽为5 MHz,时钟完美)为75 + 10 × log10 (250/5) = 92 dB。

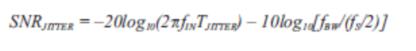

然而,ADC时钟并不完美;根据图3所示,在5 MHz所需信号带宽中的性能下降效应为x轴频率下大无用信号输入的函数。随着抖动的增加,无用信号的影响变得更加严重,随着输入频率的增加,情况同样如此。如果无用信号的幅度下降,可用SNR将按比例增加。

例如,如果在200 MHz输入下对一个满量程5 MHz无用W-CDMA信号进行采样,采用一个高质量的500 MHz时钟(如HMC1034LP6GE),且运行于整数模式下时抖动为70 fs,则附近5 MHz通道中的SNR约为91 dB。相反,如果时钟抖动降至500 fs,则同一数据转换器和信号只会表现出81 dB的SNR,相当于性能下降10 dB。

在400 MHz下把同一信号输入数据转换器,70 fs的时钟会产生88 dB的SNR。类似地,在500 fs的时钟下,SNR值会降至仅75 dB。

图3.ADC SNR与时钟抖动和输入频率的关系。

结论

为时钟生成和数据转换选择正确的组件可使设计师从给定架构中获得最佳的性能。在选择时钟发生器时要考虑的重要标准有相位抖动和相位噪底,它们会影响被驱动的数据转换器的SNR。正如分析所示,对于选定的时钟发生器,其低相位噪底和低积分相位抖动特性有助于最小化多载波应用中SNR性能在较高ADC输入频率下的降幅。HMC1032LP6GE和HMC1034LP6GE 时钟发生器在设计时即已充分考虑了数据转换器应用的需求,搭配ADI高速ADC器件使用可获得良好的性能。

这些时钟发生器以及ADI的时钟分配产品和ADC可以组合起来,打造超高性能的时序解决方案。这些产品可以通过公司网站订购,数据手册也可通过www.analog.com获取。

评论