一种带失调自校正运放的电流采样电路设计

摘要:本文介绍了一种应用在电源管理芯片中带失调自校正运放的电流采样电路设计。相对于传统的运放失调消除技术,本失调自校正运放设计无需开关电容相关技术,可节省一定的芯片面积,通过在芯片启动时自动校正输入失调,并将校正位锁存。之后,由于运放零失调,可大大提高所述电流采样电路的精度。该技术已经成功应用在数款电源管理芯片中,量产测试结果表明,采用该电路的电流采样精度小于0.2%。

本文引用地址:http://www.amcfsurvey.com/article/201607/294702.htm引言

失调电压是高性能CMOS电路设计中需要考虑的一个重要参数[1]。在实际的信道中,电路的失调电压主要是由制造工艺的不确定性和封装后的机械压力引起的。如运放的失调电压大小,主要是由输入输出级差动对的差异决定[2-3]。同时,差分输入信号本身也可能含有失调电压。失调电压在一定程度上决定了产品的性能或成品率。电流采样电路必然存在运放,由于运放失调的存在,使电流采样的精度难以提高。

1 失调消除技术

当不采用校准技术时,一个好的CMOS模拟电路在遵循版图设计规则的情况下,失调电压通常在正负10mV范围内。加大输入输出级差动对的尺寸可以减小失调电压,但这样设计的结果会使输入输出电容变得过高,严重地降低了电路的速度,同时也会明显加大版图尺寸。因此,很多高精度系统需要用电子学方法来消除失调,即在电路设计时就加入失调电压消除设计。

目前,用于减小运放失调电压的技术主要有三种:斩波技术(CHS)、自动调零技术(CAZ)以及相关双采样技术(CDS)[1]。但是斩波技术会导致运放增益下降且输入、输出调制器的延迟也应该做到与主放大器的延迟完全匹配;自动调零技术和相关双采样技术则需要独立的两个步骤,一是对运算放大器的噪声和输入失调电压进行采样,二是把含有噪声和失调电压的运算放大器的输入端或者输出端瞬间减去这部分不理想电压,其主要适用于开关电容电路,不适合连续电路应用,如电源管理电路中需持续采样电路中的电流[4]。

为了克服现有技术缺陷,本文给出了一种在电路启动阶段便有效消除失调电压的设计方法,从而使之在电路正常工作时一直保持零失调状态。即电流采样电路在工作时,其运放一直处于“零”失调状态,从而大大提高采样精度。

2 电路分析与设计

2.1 整体电路分析

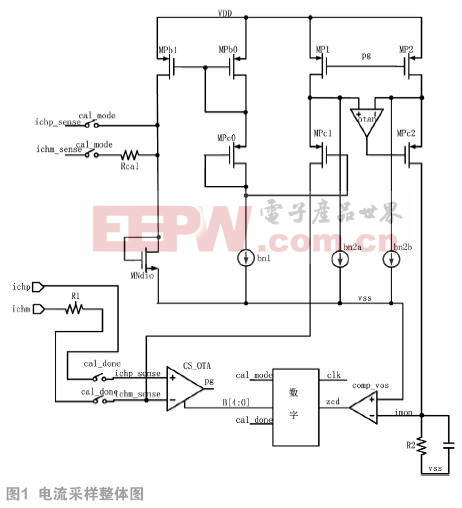

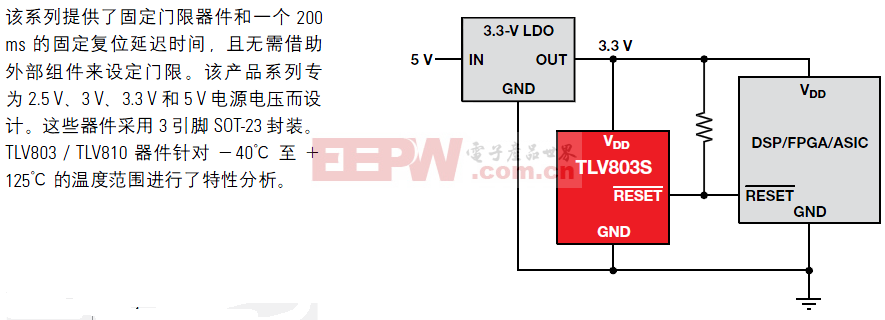

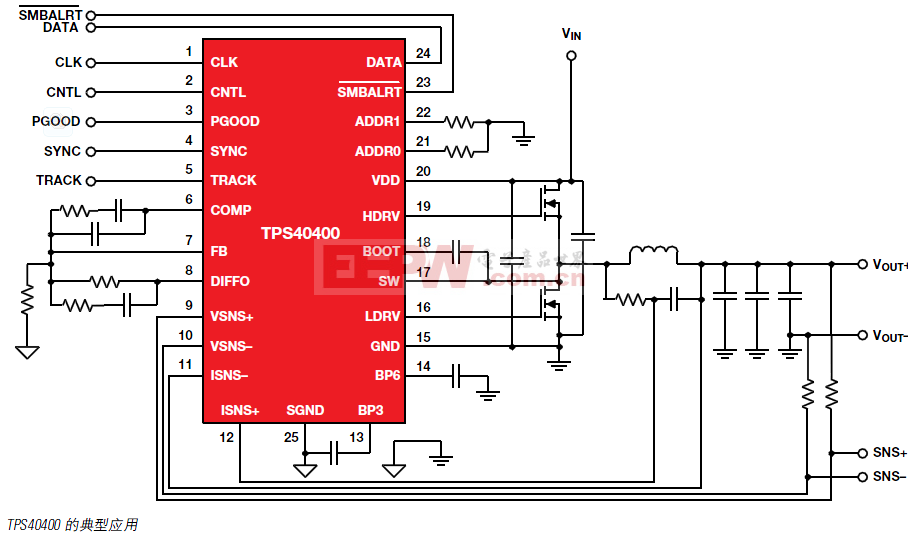

如图1所示,整个电流采样功能模块包含了偏置电路(为了使图看起来简单,用理想电流源代替)、电流采样支路、核心运放CS_OTA、共源共栅电流镜部分中的运放otan、比较器comp和数字部分(含计数器)等功能模块。

如图1所示,芯片启动时,自动进入校正模式,数字部分输出节点cal_mode的电压Vcal_mode=1, 输出节点cal_done的电压Vcal_done=0(cal为校正计算calculation的缩写),校正计算位b[4:0]置为00000。其中,电流源bn1为MPb0和MPb1两条支路提供偏置电流,电流源bn2a和bn2b为MP1和MP2两条支路提供直流静态偏置电流。

由于Vcal_mode=1,运放CS_OTA输入两端通过图中左上角的两个开关接到电阻Rcal两端,而二极管连接的MOS管MNdio用来给运放CS_OTA提供直流偏压(可根据需要的直流静态点来设置二极管连接的MOS管的串联个数)。此时由于运放CS_OTA内部固有的失调(失调分析见下节2.2),将导致运放输入两端存在约-9mV的差,即Vos=V(ichp_sense, ichm_sense)=-9mV,Vos将施加到电阻Rcal两端,电流Vos/Rcal通过PMOS管MPc1从PMOS管MP1处抽取电流,然后该电流通过MP1镜像到MP2支路,之后施加到电阻R2上,电阻R2上的压降即为Vimon=Vos*(R2/Rcal)=Vos*50(R2的阻值假设为Rcal的50倍),节点imon的电压Vimon即为放大的失调电压。

之后,随着时钟信号clk的变化,计数器输出b[4:0]将从00000一位一位地增加,如00000 -> 00001 ->00010…,从而使失调电压V(ichp_sense, ichm_sense)慢慢降为0,Vimon也慢慢降为0,当V(ichp_sense, ichm_sense)和Vimon非常接近0时,比较器COMP_Vos(比较器内部输入端加入1-2mV的失调)输出的zcd(zero current detect)将变高,则输出节点cal_done的电压信号Vcal_done(校正结束)将随之变高,计数器将锁定此时的输出位b[4:0]。

当校正结束后,图1的电流采样电路处于电流采样状态,通过采样引脚ichp和ichm两端的电压Vsense=V(ichp,ichm),然后把Vsense/R1的电流通过MP1镜像到MP2支路,施加到电阻R2上,通过电阻R2上的电压即可得到精确的采样电流。

2.2 运放失调分析

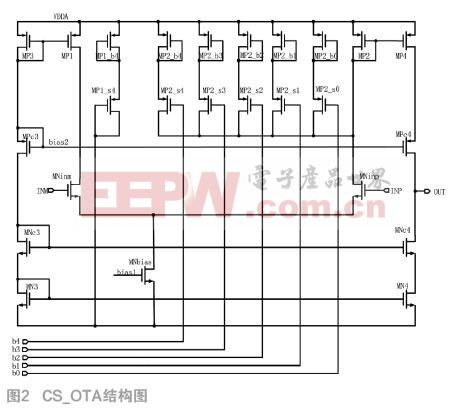

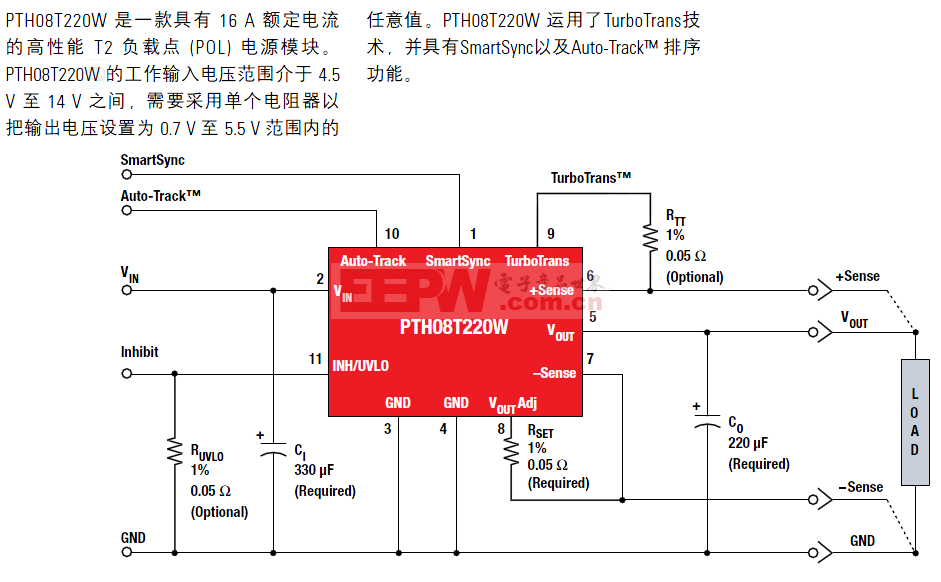

为了使增益和带宽有良好折中,本文中的核心运放CS_OTA采用了如图2所示的折叠式二级运算放大器。

影响该运放等效输入失调电压的主要有输入对管MNinp和MNinm,负载管MP1和MP2。然后通过如下公式可计算出等效输入失调电压[5]:

(1)

(1)

(2)

(2)

(3)

(3)

(4)

(4)

如图2所示,为了能够使运放失调得到校正,在其中一条负载管MP2支路上并联一些小尺寸的管子,来引入失调,通过trim位步进的调整,使输入失调慢慢减少到0。

3 结果分析

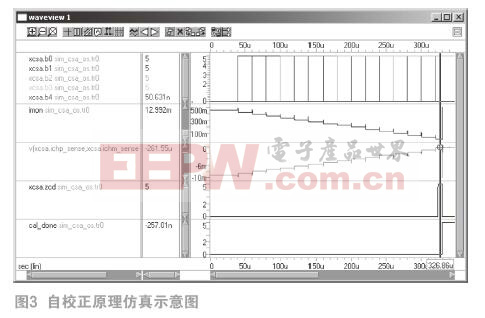

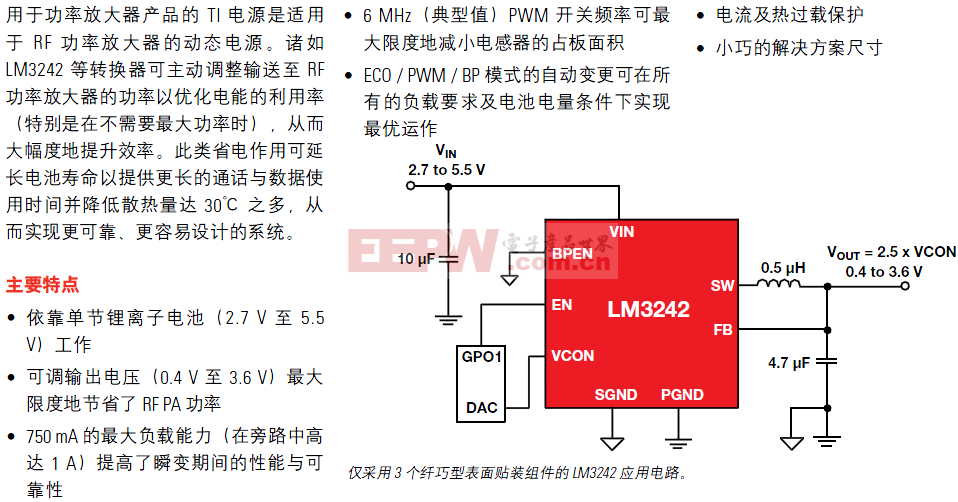

图3给出了本文的功能性仿真示意图,可以看出,刚启动时,运放输入两端的等效失调电压为9mV,通过时钟控制计数器使trim位b[4:0]每周期跳变一位,使输入端的失调电压慢慢减小,失调电压接近0时,通过镜像使失调电流到电阻R2上,其上的压降Vimon也慢慢减少,当Vimon接近0的时候,比较器输出端ZCD变高,校正标志位Cal_done变高,校正结束。

采用本电路结构的电流采样电路已经成功应用于数款电源管理芯片中,量产测试结果表明,其电流采样精度小于0.2%。

4 结论

本文首先分析了运放失调产生的原因,随后给出了适合在电源管理芯片中带失调自校正运放的电流采样电路的设计,之后分析了电路工作原理和失调计算方法。该电路结构设计简单,无需开关电容相关技术,可节省一定的芯片面积,同时可使失调电压降到可控范围内,非常适合大规模工程应用;之后给出的仿真结果图,使电路工作过程一目了然。采用该结构的电源管理芯片,量产测试结果表明,其电流采样精度小于0.2%。

参考文献:

[1王松林,张树春,叶强,等.一种采用改进自调零技术的误差放大器设计[J].复旦学报, 2010, 49(6): 667-673.

[2]贾子涵,冯全源,庄圣贤. 适用于DC-DC开关电源的振荡器设计[J].电子元件与材料, 2015, 34(3): 29-32.

[3]苏丹,胡永贵,徐辉.一种同步降压型DC-DC转换器驱动电路设计[J].微电子学, 2014, 44(6): 709-712.

[4]LEE C F, MOK P K T. A monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique[J].IEEE JSSC, 2004,39(1):3-14

[5]Behzad Razavi. Design of analog CMOS integrated circuits[M]. Boston: McGraw-Hill, 2001:376-389.

本文来源于中国科技期刊《电子产品世界》2016年第7期第65页,欢迎您写论文时引用,并注明出处。

评论