现可使用60 GHz回程链路提升蜂窝容量

摘要:基于Xilinx Zynq SoC和ADI V频段芯片组的完整60 GHz双向数据通信方案能够提供小型蜂窝回程市场所需的性能和灵活性。

本文引用地址:http://www.amcfsurvey.com/article/201605/291775.htm全球蜂窝网络上对数据的需求不断增长,迫使运营商想法设法在2030年前将容量提升5000倍[1]。要实现这一目标,需要将通道性能提升5倍、分配频谱提高20倍、蜂窝基站数量增加50倍。

许多此类新型蜂窝将布置在室内,因为这里是大部分流量的来源,而光纤则是将流量回传到网络的首选。但还有许多室外场所无法连接光纤或光纤连接成本过高,对于这种情况而言,无线回程是最可行的替代方案。

现可使用免执照的频谱5 GHz,而且无需提供视线(LOS)路径。但是其带宽有限,而且由于大流量和宽带天线,无疑会受到该频谱其他用户的干扰。

对于满足容量需求所需的数以千计的室外蜂窝,60 GHz通信链路正在成为提供此类回程链路的有力竞争者。该频谱也属于免执照频段,但与6 GHz以下的频率不同,它包含高达9 GHz的可用带宽。此外,高频允许窄而集中的天线场型,可在一定程度上提高抗干扰性,但它需要LOS路径。

基于FPGA和基于SoC的调制解调器越来越多地用于各种无线回程解决方案,这是因为使用这种调制解调器的平台模块化且可定制,从而能够降低OEM的总成本。对于这些链接的无线电部分,收发器已集成在基于硅的IC中,并且封装为低成本的表贴器件。

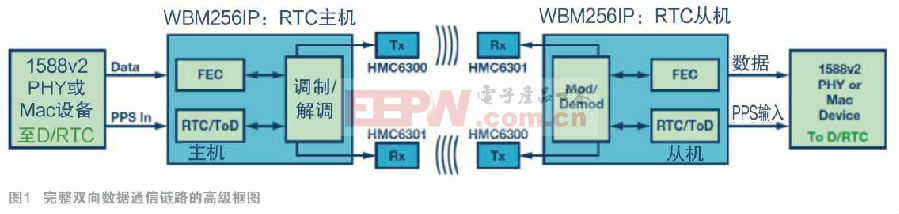

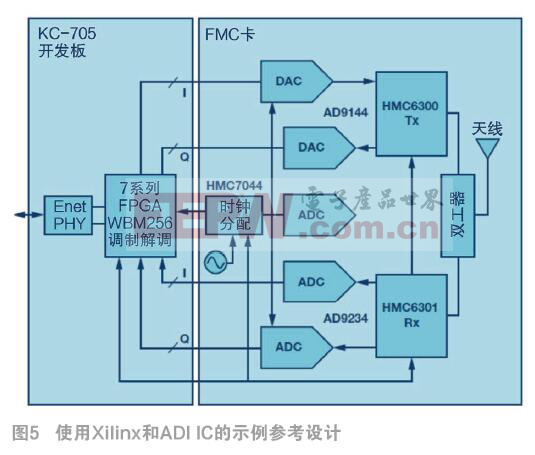

可使用商用器件构建完整的60 GHz双向数据通信链路,如图1中的解决方案所示。该设计由Xilinx和Hittite微波公司(现为ADI公司的下属公司)研发,包括Xilinx调制解调器和ADI毫米波无线电。该链路满足小型蜂窝回程市场的性能和灵活性要求。

如图1所示,创建链路需要两个节点。每个节点都包含一个发送器(带调制器)及其关联的模拟发送器链、一个接收器(带解调器)及其关联的模拟接收器链。

调制解调卡与模拟和分立式器件集成。它包含以数字方式实施的振荡器,能够确保频率合成的精度,并且所有数字功能均在FPGA或片上系统(SoC)上执行。这种单载波调制解调器内核可支持从QPSK到256 QAM的调制,通道带宽高达500 MHz,能够实现高达3.5 Gbps的数据速率。该调制解调器还可同时支持频分双工(FDD)和时分双工(TDD)传输方式。稳健可靠的调制解调器设计方法能降低本振的相位噪声影响。为改善性能和链路预算,内置强大的低密度奇偶校验(LDPC)编码。

毫米波调制解调器

毫米波调制解调器可帮助基础设施供应商为其无线回程网络开发灵活且成本优化的可定制链路。它具有完全自适应、低功耗、小尺寸特性,可用于部署室内和全室外点对点链路以及点对多点微波链路。借助该解决方案,运营商能够构建可扩展、现场可升级的系统。

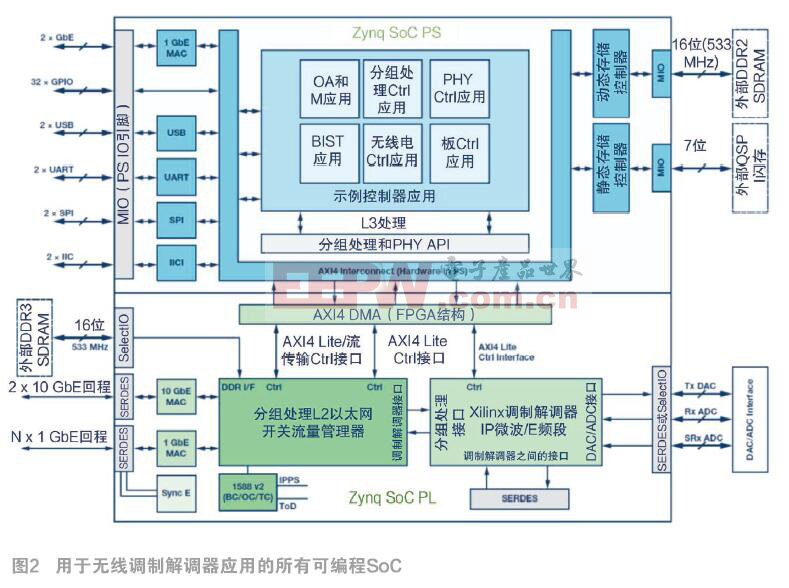

图2详细说明在基于SoC的解决方案中实施的数字调制解调器。平台的可扩展处理系统(PS)位于可编程逻辑(PL)旁,包含双ARM Cortex-A9内核,后者带有集成式存储器控制器和供外设使用的多标准I/O。

该SoC平台用于执行各项数据和控制功能并实现硬件加速。图2所示的是集成式毫米波调制解调器以及配套的PHY、控制器、系统接口和包处理器。但是,用户可以根据所需的架构插入、更新或移除不同的模块。例如,用户可以选择实施XPIC组合器,这样可以将该调制解调器与另一个调制解调器以交叉极化模式配合使用。解决方案在PL中实施,使用SERDES和I/O作为各个数据路径的接口,比如调制解调器与包处理器之间的接口、包处理器和存储器之间的接口、调制解调器彼此之间的接口或DAC/ADC的接口。

该调制解调器IP的一些其他重要特性包括:通过自适应编码和调制(ACM)功能保持链路连续工作的自动无损和无误状态切换、可改善RF功率放大器效率和线性的自适应数字闭环预校正(DPD)、能够保持时钟同步的同步以太网(SyncE)以及里德-所罗门或LDPC前向纠错(FEC)。FEC根据电路要求选择。LDPC FEC是无线回程应用的默认选择,而对于去程等低延时应用而言,Reed-Solomon FEC则更加适合。

LDPC实施方案经高度优化,并利用FPGA并行性帮助编码器和解码器完成计算。这可显著改善SNR。您可通过改变LDPC内核的迭代数量来应用不同级别的并行性,进而优化解码器的尺寸和功耗。此外,您还可根据通道带宽和吞吐量约束条件为设计建模。

该调制解调器解决方案还配备用于显示和调试的图形用户界面(GUI),并可提供通道带宽选择、调制方式选择等高级功能以及硬件寄存器设置等低级功能。为让图1所示的解决方案实现3.5 Gbps的吞吐量,该调制解调器IP需要以440 MHz的时钟速率运行。它将五个千兆位收发器(GT)用于连接接口,以支持ADC和DAC,并把另外一些GT用于10 GbE有效载荷或CPRI接口。

毫米波收发器芯片组

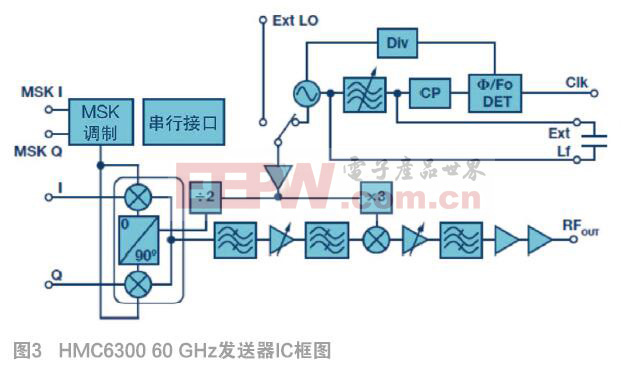

ADI公司针对小型蜂窝回程应用,优化了其在该设计中使用的第二代硅锗(SiGe) 60 GHz芯片组。发送器芯片是一款完整的模拟基带转毫米波上变频器。采用以250MHz步进覆盖57 GHz到66 GHz的改进型低相位噪声频率合成器,可支持至少64 QAM的调制。输出功率已经提升到大约16 dBm线性功率,而集成式功率检测器则可监测输出功率,使其不超过法定限值。

该发送器芯片可提供对IF和RF增益的模拟或数字控制。在使用更高阶调制的情况下,有时需要模拟增益控制,因为对幅度调制而言,离散增益改变可能会出错,导致出现误码。内置SPI接口可为数字增益控制提供支持。

对于在窄通道中需要更高阶调制的应用而言,可以向发送器中加入拥有更低相位噪声的外部PLL/VCO,并使内部频率合成器旁路。

图3显示了最高支持1.8 GHz带宽的发送器芯片的框图。MSK调制器选项可实现速率高达1.8 Gbps的低成本数据传送,而无需使用高成本、高功耗的DAC。

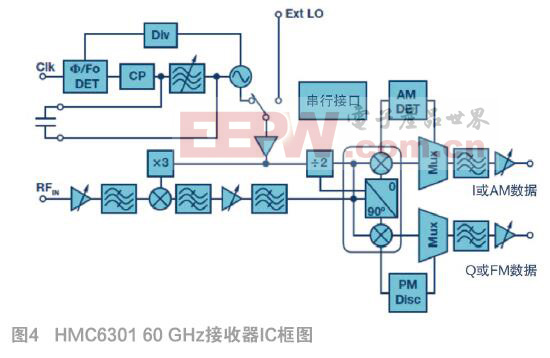

接收器芯片是该器件的辅助器件,同样经过优化,能够满足小型蜂窝回程的严苛要求。该接收器的特点是能够将输入P1dB大幅提升到-20 dBm,并将IIP3提升到-9 dBm,从而处理短程链路,短程链路中碟形天线具有高增益,会在接收器输入端产生高信号电平。

其他主要特性包括:噪声系数在最大增益设置下低至6 dB;可调低通和高通基带滤波器;合成器与发送器芯片中的新型合成器相同,能够在57 GHz到66 GHz频段支持64 QAM调制;对IF和RF增益的模拟或数字控制。

图4显示了接收器芯片的框图。请注意,该接收器还包含一个AM检测器,用以解调开关键控(OOK)等幅度调制。此外,还可使用FM鉴频器解调简单的FM或MSK调制。这就是用于为QPSK恢复正交基带输出和解调更复杂的QAM调制的IQ解调器之外的附加功能。

发送器和接收器均采用4mm×6mm BGA型晶圆级封装。借助这些表贴器件,可实现回程应用无线电板的低成本制造。

图5所示的是示例毫米波调制解调器和无线电系统的框图。除FPGA、调制解调器软件和毫米波芯片组外,该设计还包含一些其他组件。其中包括双通道12位1 GSPS ADC;最高2.8 GSPS的四通道16位TxDAC;以及超低抖动时钟合成器(支持ADC和DAC IC上使用的JESD204B串行数据接口)。

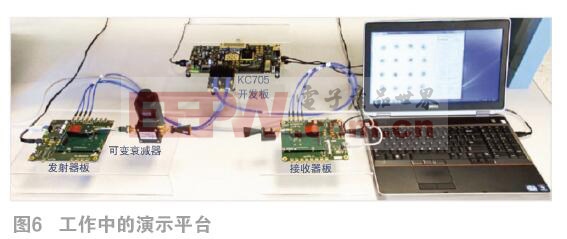

演示平台

图6所示的平台由Xilinx和ADI公司共同创建,用于演示目的。该实施方案包括Xilinx开发板上的FPGA调制解调器、工业标准FMC板(包含ADC、DAC和时钟芯片),以及两块无线电模块评估板。

该演示平台包括用于调制解调器控制和视觉显示功能的笔记本电脑,以及用于复制典型毫米波链路路径损耗的可变RF衰减器。开发板上的FPGA可执行WBM256调制解调器固件IP。开发板上的工业标准FMC夹层接插件可用于连接基带板和毫米波无线电板。

毫米波模块可卡合在基带板上。模块具备用于60 GHz接口的MMPX连接器以及用于可选用外部本振的SMA连接器。该平台包含在频分双工连接的每个方向对应的250 MHz通道中演示高达1.1 Gbps点对点回程连接所需的全部硬件和软件。

模块化和可定制

由于FPGA高度模块化且可定制,因而能够降低为无线回程应用构建平台的成本。为小型蜂窝回程市场的毫米波调制解调器解决方案选择商用器件时,请选择高能效的FPGA/SoC和高性能的宽带IP内核。高速也是为宽带通信和开关功能选择GT时应考虑的一个因素。此解决方案扩展能力出色,支持多种产品种类,包括以每秒数百兆位运行的低端小型蜂窝回程产品,以及同一硬件平台上的3.5 Gpbs回程产品。

至于无线电部分,收发器IC封装在表贴器件中,降低了制造成本。市场上的器件可满足小型蜂窝部署无线回程需求的功耗、尺寸、灵活性和功能要求。您还可采购专为完善无线回程链路配备的高性能数据转换器和时钟管理IC。

参考文献:

[1]关于超高容量网络的演进及颠覆性愿景.国际无线工业联盟(IWPC),2014年4月.

本文来源于中国科技期刊《电子产品世界》2016年第5期第77页,欢迎您写论文时引用,并注明出处。

评论