10W高线性802.11n功率放大芯片设计

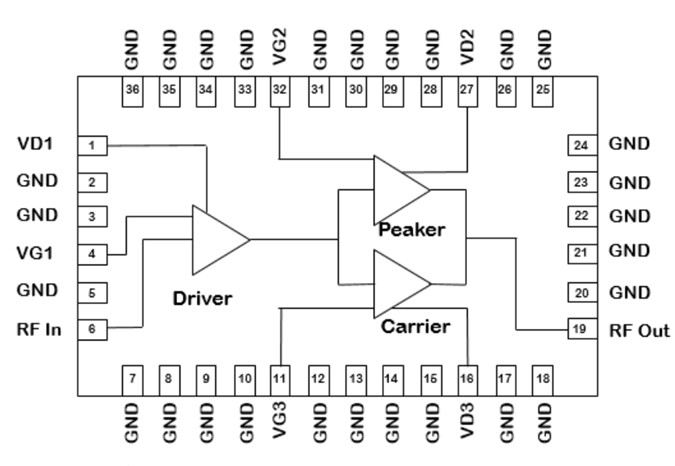

摘要:本文介绍了一款用于无线局域网802.11n的10W功率放大芯片。该芯片具有高功率、高增益、高效率和高集成度的特点,并且使用方便。芯片采用GaAs HBT技术,芯片面积仅为10mm×10mm。功率放大器采用了热分流式结构,饱和输出功率可达41dBm,功率附加效率达到40%,功率增益为38dB。此外芯片内部设计了50欧姆的输入输出匹配电路与片内ESD保护电路,方便用户安全使用。

本文引用地址:http://www.amcfsurvey.com/article/201603/288909.htm引言

802.11n是宽带无线局域网(WLAN)的一种传输标准。在WLAN组网时,可以利用无线桥接技术将两个不同物理位置,不方便布线的用户连接到同一局域网内。但是由于WLAN自身发射功率较低,桥接的距离非常有限。因此在为桥接路由器设计大功率、高线性、符合802.11n要求的功率放大器是非常有价值的。

在实际应用中,为满足传输距离要求,需要线性输出2W的功率放大器。为得到2W的线性输出,通常功率放大器的饱和输出功率需要达到10W以上。10W功率放大器通常是由电路模组实现的,体积大,一致性不高。本文介绍的是一款10W功率放大芯片,芯片采用10×10×1.1mm3的LGA封装,相比于电路模组,大大节约了电路板面积,同时在稳定性、一致性方面具有很大优势[1]。

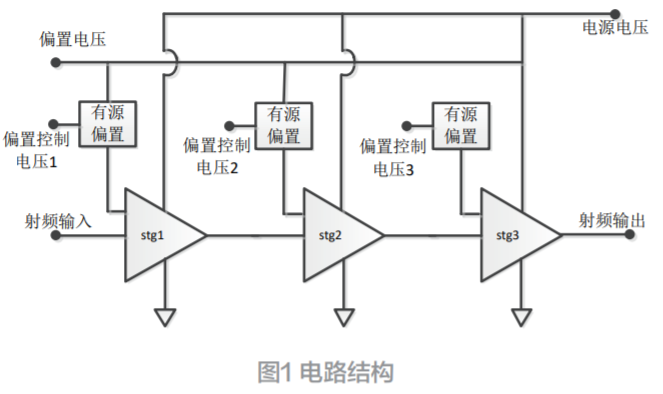

1 电路总体结构设计

考虑到放大器的输入功率限制,10W的功率放大器必须具有高增益。设计的增益指标定在35dB以上。考虑到电路的级间匹配损耗,整个功率放大器需要由4级放大电路构成[2]。

为降低芯片的使用难度,将输入、输出匹配电路设计在芯片内部,做到输入、输出端口50欧姆阻抗匹配。

该功率放大器工作在2.4GHz,匹配电路需要占据一定的芯片面积。设计的面积指标定为:放大模块与匹配电路总面积控制在10mm×10mm以内。最终芯片选择的也是10×10×1.1mm3的LGA封装。

为进一步降低芯片使用难度,芯片设计时,尽量减少外围元器件。外围管脚尽量简化,仅有射频输入、射频输出、直流供电与控制端口。

2 末级放大电路设计

在系统设计中,通常阻抗变换比可以做到1:10。也就是说在50欧姆系统中,从功放输出端看出去的负载阻抗最小可以做到50欧姆的1/10,也就是5欧姆。根据![]() 且

且![]() ,可以得出

,可以得出![]() 。考虑到电压利用效率,芯片的末级供电电压选择为12V。

。考虑到电压利用效率,芯片的末级供电电压选择为12V。

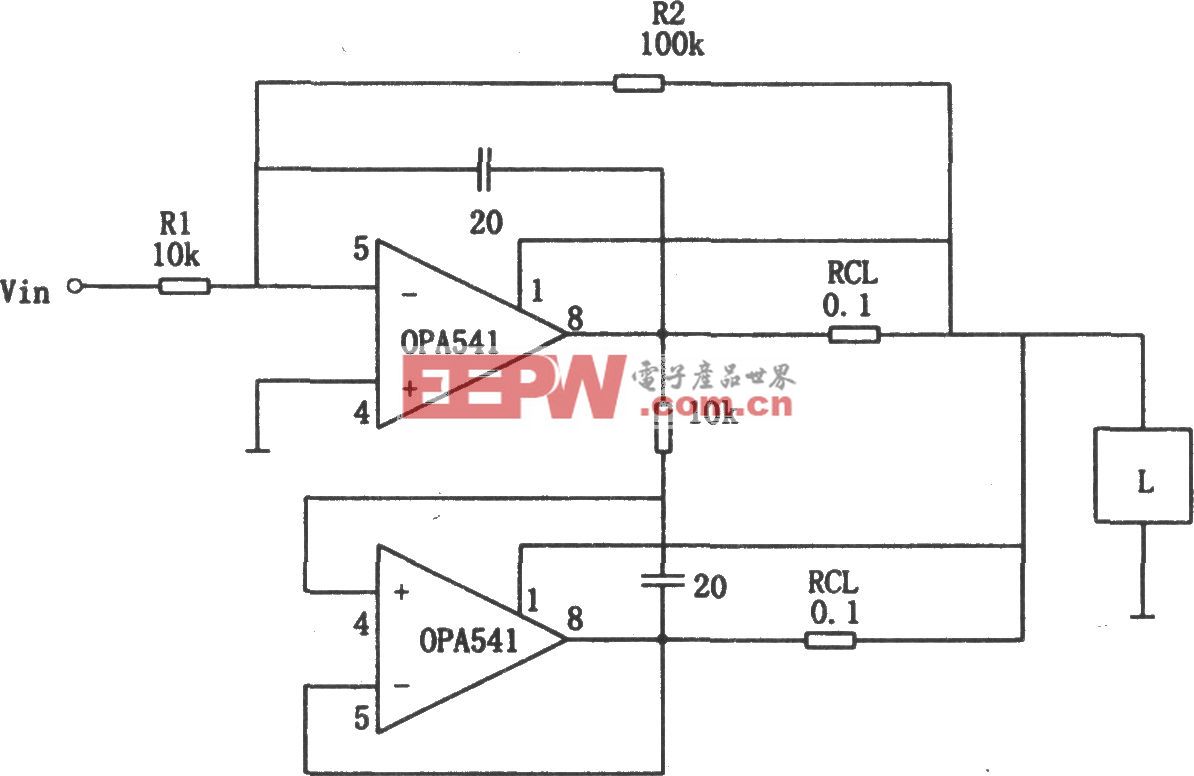

芯片末级供电12V,那么输出电压的摆幅将达到20V以上。单个GaAs HBT晶体管耐压通常在12V-14V,是无法承受这么高的电压变化的[3]。因此芯片末级放大电路采用Cascode结构,利用两个晶体管分担电压。

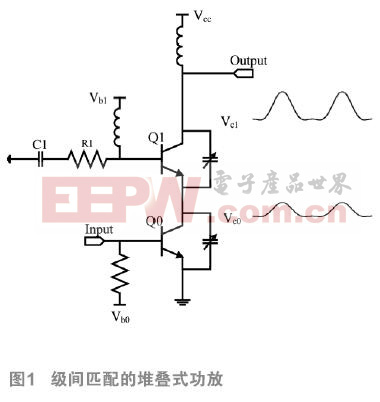

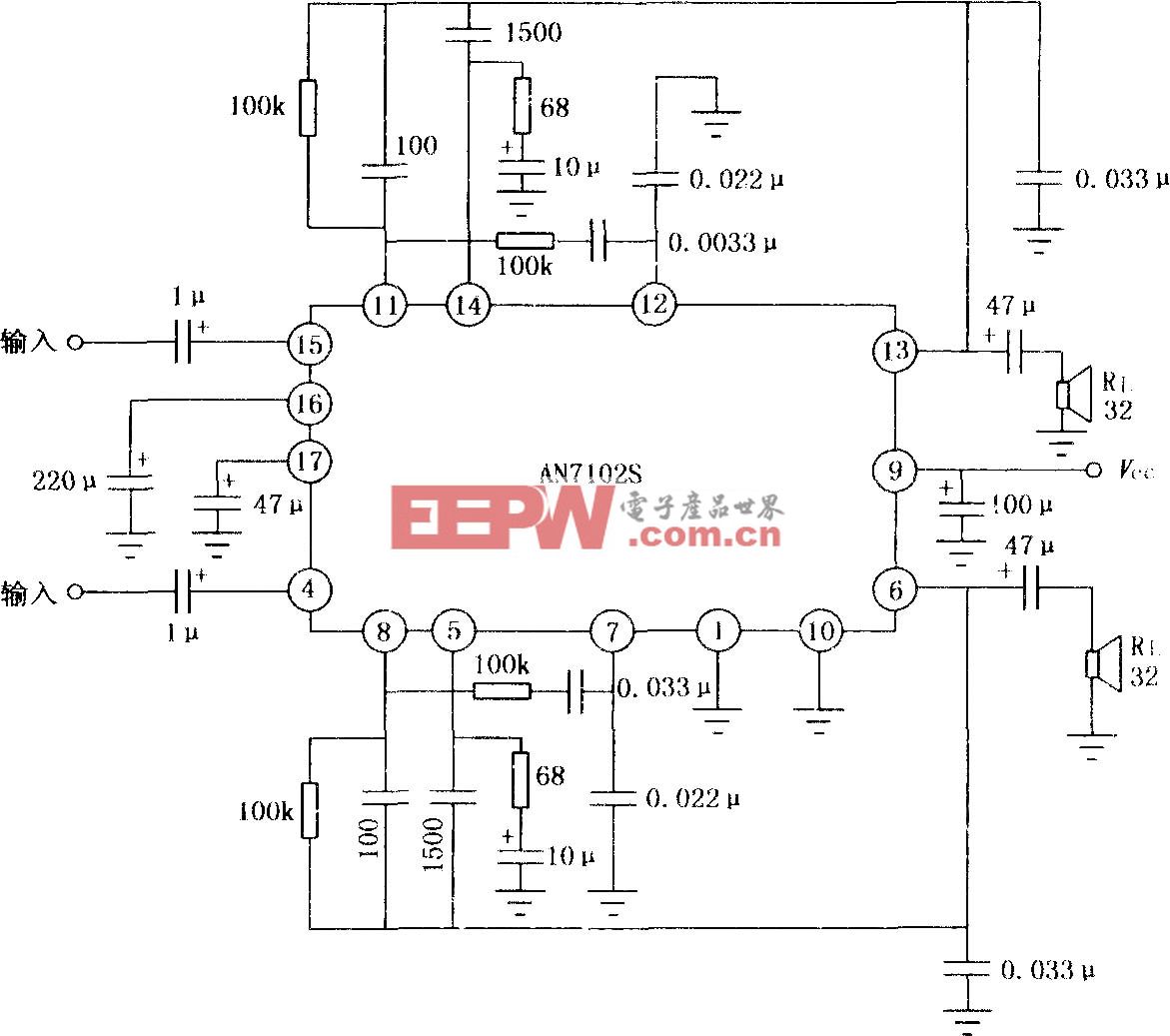

本设计中采用了一种新颖的Cascode结构,如图1所示,Q1的基极带有阻容元件,这是一种级间功率匹配技术[4-5]。在普通Cascode结构电路中,晶体管Q1的基极对于射频信号是接地的,因此从Q1的发射极看到的阻抗非常小,也就是说晶体管Q0的负载阻抗非常小。这导致绝大部分电压将由晶体管Q1承受,两个晶体管分担电压的效果不理想。而在本电路设计中,该电路结构配合输出匹配电路,可以使晶体管Q0与Q1平均分摊电压摆幅。这样两个晶体管都处于良好的工作状态下,可以提升Cascode放大器的线性与效率。

3 供电方式设计与控制端设计

末级放大器需要采用12V供电。然而对前级放大器而言,只需要5V的工作电压就可以驱动末级放大器。如果统一采用12V供电,会降低整个放大器效率。而且高供电电压会大大增加ESD保护电路的面积。因此芯片设计时采用了12V与5V两路直流供电。

此外芯片还带有偏置控制端口。该端口与各级放大器的偏置电路相连,可以通过该端口来关断功放的偏置电路,达到关闭整个功率放大器的效果。

4 热分流设计

大功率的功率放大器芯片工作时,巨大的热功耗会导致HBT温度的急剧上升。其实质为电子、空穴以及半导体晶格组成的热动力系统发生变化[6]。HBT工作于放大状态时,基极-集电极之间的耗尽结产生的电场最大,电流密度大。在强电场作用下,载流子被加速并从电场中获得能量,致使其平均能量比平衡时高出很多,从而载流子温度升高,相应的电学特性发生变化[7]。

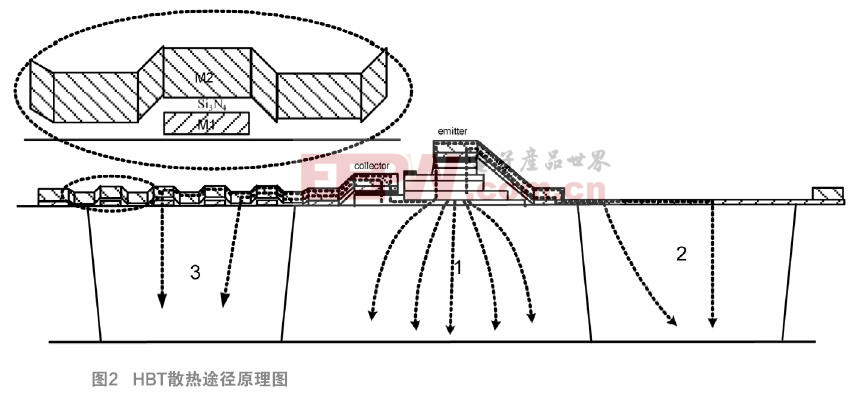

为保证电学特性的稳定,必须采用合理的散热方式降低晶体管温度。图2为HBT的热流流动图。其中,散热途径1为传统的散热方式,即晶体管通过衬底散热。途径2采用将发射极与金属连接的方式进行散热,可以采用金属银,其热导率为420W/ m•K ,此方法提供了快速的散热通道。由于在HBT功放设计中,发射极通常接地,因而,此种连接方式并不会影响电气的连接。途径3为本文提出的增加的散热途径。由于集电极的热量最大,实际温度最高,因而也是最需降温的部分,采用正交排列的双层金属条,尽管在电气上没有互联,热量却可以通过金属条再次散入背孔中,增加的散热路径为晶体管提供更好的散热环境,从而可以有效抑制器件的温升。

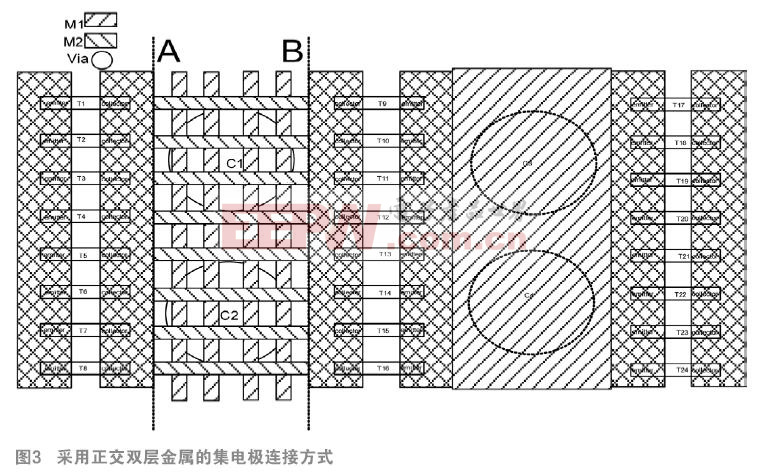

图3为3组功率单元的版图示意图。其中晶体管T1~T8的集电极与T9~T16集电极通过金属层2相连,其中金属层1与背孔C1、C2直接相连,而位于上层的金属层2与其正交放置,如区域AB所示。金属层1与2之间由于存在绝缘介质Si3N4,因而电气上并未直接连接,这与放大器中集电极的偏置方式一致。此外,由于采用正交方式,此种分流技术并没有增加版图面积,且金属层1与2的重叠面积最小,在优化散热路径的目标下最大程度减小耦合的寄生电容,从而对放大器射频性能的影响可以忽略。

5 芯片测试结果

该芯片采用2微米的GaAs HBT技术与10×10×1.1mm3的LGA封装。

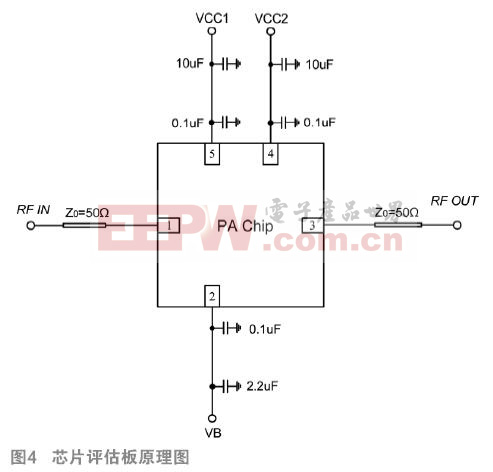

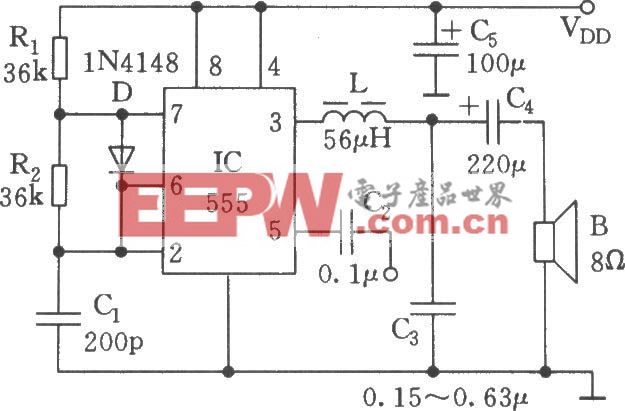

图4是芯片评估板原理图,图5是评估板照片。芯片只有5个管脚,而且芯片所需要的外围电路非常简单。

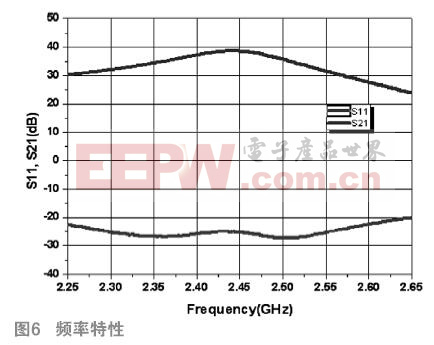

芯片的频率特性测试结果如图6。在2.4GHz-2.5GHz频率范围内,芯片的回波损耗都在-20dB以下。在802.11n系统的工作频点,功放增益达到38dB。

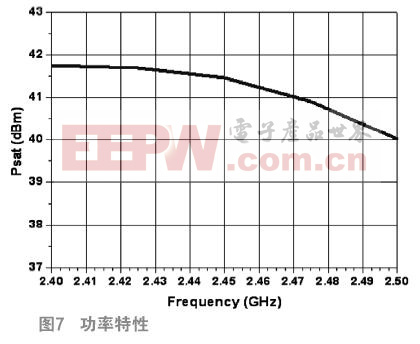

芯片的饱和输出功率如图7。在2.4GHz频点上饱和输出功率达到41dBm,即12W。在2.4GHz-2.5GHz频率范围内,饱和输出功率都在10W以上。

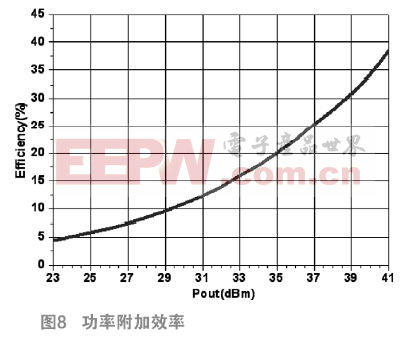

芯片的功率附加效率随输出功率的变化如图8所示,芯片效率可以达到40%。

用信号源产生802.11n信号输入功率放大器测试板,使用Agilent频谱分析仪N9020A测量EVM。在2W输出时,EVM为-30dB,满足802.11n线性度要求。

6 结论

该芯片的输出功率可以达到12W,可以满足多数桥接设备的需求。同时在电路设计中采用了堆叠式功率放大器的功率匹配技术以及热分流设计,提高了整个功率放大器的性能。从评估板设计可以看出,使用该芯片非常简单。输入输出匹配均在片内集成,此外芯片内部还集成了ESD保护电路,大大提高了芯片的可靠性。

参考文献:

[1] 尤览.射频放大器的效率增强与线性化技术研究[D]:[博士学位论文].合肥:中国科学技术大学电子工程与信息科学系,2011

[2] Shifrin M, Ayasli Y, Katzin P. A new power amplifier topology with series biasing and power combining of transistors [C]. IEEE Microwave and Millimeter-Wave Monolithic Circuits Symposium. 1992. 39-41

[3] Zhang L, Li M, Shi Y, et al. A Modified GP large-signal model for InGaP/GaAs HBT and direct optimization extraction methodology [C]. 10th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2010. 1856-1858

[4] Jeong J, Pornpromlikit S, Asbeck P M, et al. A 20 dBm Linear RF Power Amplifier Using Stacked Silicon-on-Sapphire MOSFETs [J], IEEE Microwave and Wireless Components Letters, 2006, 16(12): 684-686

[5] Lei M F, Tsai Z M, Lin K Y, et al. Design and Analysis of Stacked Power Amplifier in Series-Input and Series-Output Configuration [J]. IEEE Transactions on Microwave Theory and Techniques, 2007, 55(12): 2802-2812

[6] D. 皮茨,L. 西索姆著. 传热学[M]. 第二版. 葛新石译. 北京:科学出版社. 2001:1-16

[7] Mohammadi F A, Meres K and Yagoub M C R. Rigorous thermal treatment of heat generation and heat transfer in GaAs based HBT based device modeling [C]. IEEE Micro-Electronics and Micro-Systems, EuroSimE. 2005: 604-608

本文来源于中国科技期刊《电子产品世界》2016年第3期第50页,欢迎您写论文时引用,并注明出处。

评论