基于FPGA的汽车视频和图形控制系统设计

LCD显示器真是无处不在,在家庭、超市、体育馆以及汽车内你都可以见到它们的身影。无疑车载LCD显示系统是增长最快的市场。增长的动力包括:不断下降的显示器价格、不断提升的用户体验、更多的产品性能以及车内消费类产品的集结。

本文引用地址:http://www.amcfsurvey.com/article/196704.htm典型的图形显示系统一般都是利用标准的特殊应用标准处理器(ASSP)或者定制的特殊应用集成电路(ASIC)作为控制器来构建的。但汽车图形设计师在利用这些器件构建系统时遭遇到了不小的麻烦,其中包括:较短的产品生命周期,基于PC的系统总线接口,无法适应新标准和新显示器类型等。所有这些问题都限制了设计在其它应用中的重用可能性。

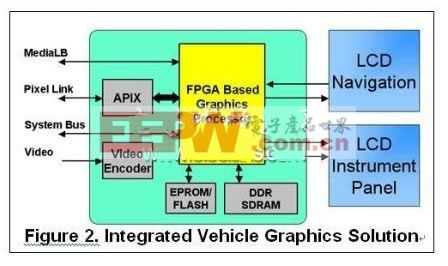

图1给出了车载图形/视频系统的一个典型实例。图的左侧列出了用于驱动图形系统的一些不同输入信号。本例包括了一个MediaLB接口,一个用于视频的两线像素链路收发器,一个普通系统接口总线和一个NTSC/PAL视频编码器。一旦视频和图形信息进入系统,就由通用CPU执行处理,或者在不同的系统架构下被直接送到图形处理器。此外,绝大多数设计还含有用于程序存储的闪存以及用于存储页面和视频信息的SDRAM。

图1:典型的图形/视频系统架构。

图形处理器可以是ASSP、定制ASIC或者现场可编程门阵列(FPGA)器件。根据具体实现的不同,一个系统中可能会含有多台显示器(如图所示),这时还需要额外的逻辑资源来管理各种信号以便支持每台显示器正常工作。

如上所述,设计师在汽车设计中采用ASSP图形控制器时会遇到一些阻碍,具体包括:

1. PC和消费电子产品通常具有非常短的生命周期,但汽车市场具有很长的生产周期和支持需求,它们无法接受生命周期结束时强制发生的变化。

2. 采用硬连线的ASSP或ASIC器件无法象传统系统那样支持新兴的或者派生的视频和图象标准。

3. 硬连线系统也很难适应不同的显示器类型,其不适应性具体表现在分辨率、长宽比或显示器信号接口方面。

4. 绝大多数ASSP器件采用的都是PC总线接口,比如AGP、PCI 和PCI Express。如果要在内部系统总线和ASSP图形器件之间构建定制接口,汽车设计师还将面临额外的成本和复杂性问题。

ASIC的单片价格确实相当低,但是开发成本非常高。其掩膜成本可达数百万美元,如果需要改变设计以支持新标准或者新功能,则掩膜费用还得成倍增加。

以多用途为特质的FPGA器件加上商用化知识产权(IP)能够实现几乎所有的图形系统功能,包括视频控制器、RISC处理器、显示器接口、总线标准和不同的视频输入标准等,而且这些功能全都可以集成在一个器件上。

图2:集成式车载图形解决方案。

图2是利用FPGA实现的高集成度实例。该设计无需使用外部MediaLB器件,而是在内部FPGA逻辑中处理MediaLB协议。RISC处理器则是以基于IP的32位软核处理器形式整合在里面。再加上图形/视频内核模块IP就实现了完整的设计,包括支持触摸屏输入、LCD背光控制、存储控制器和多台显示器。该设计通过将所有主要的系统功能集成到FPGA中而大大减少了设计中的零部件数量。利用带内置非易失性启动闪存的FPGA还能节省其他更多的器件。

图形系统的硬件实现是总项目的一部分。设计师必须将精力集中到图形控制器的功能上,以便为设备找到最佳的解决方案。例如,客户信息显示器(CID)可能只需要显示文本消息和基本图形,而一系列玻璃仪表板则需要高分辨率平滑图形显示,因为实际上它代表着用CID来替代物理度量和仪器测量。一些仪器板和导航系统也有实时视频显示器用于支持后视(rear-view)摄像视频,这种显示器需要一个能够支持画中画和实时视频并且不能降低其他图像质量的图形控制器。另外,处理多路视频流和输入所需的灵活性也是其典型要求。

在实现图形系统之前有许多问题需要回答,因为每一项都会影响最终的硬件和IP内核的实现。这些问题包括:

1. 数据源究竟是视频流,还是以图形方式提供的输出,或者是两者的结合,或者两者都有?如果是视频流,有多少路视频流,分辨率是多少?

2. 最终的图像是2维还是3维?

3. 用的是哪种显示器技术,是液晶? 等离子? 还是视频?总共多少台显示器,分辨率多少?

4. 采用什么样的应用软件接口,使用的方便度如何?

5. 该应用是否需要可扩展架构,以便满足未来的发展和产品分级?

6. 需要支持多个视频页面吗?如果需要,需要多少?

7. 需要支持图像缩放吗?倍率多少?如果要求缩放,还需要具备剪辑功能。

8. 需要用于支持高速图形性能的Bitblit功能吗?设计需要水平和垂直Bitblit选择吗?

9. 系统需要什么样的存储器和总线接口?

10. 最后就是是否需要支持未来的系统扩展?

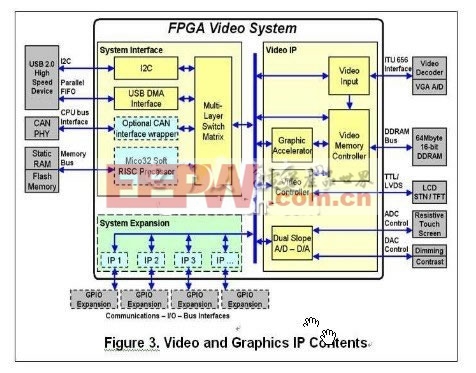

图3:视频和图形IP内容。

图3给出了一个模块化二维图形和视频IP内核的例子。该IP代表了当前FPGA图形IP内核所能提供的功能和特征。这种高速图形内核是专门为了嵌入进FPGA系统而开发的。其存储控制器可以连接SDRAM或DDRAM,具体取决于应用性能和成本预算。这种IP内核带有可选的视频输入和bitblit模块,可以用设计所需的特定性能和功能进行配置。显示控制器可以控制采用任何显示技术的单显示器或双显示器。该种内核具有通用的内部32位AMBA总线,可以方便地与其他内部IP内核接口, 或者通过FPGA的I/O与外部逻辑相连。

评论