基于FPGA的扫频信号源的研究与设计

2.2 相位累加器的设计

相位累加器由加法器和寄存器构成。加法器完成加法,寄存器将加法器的结果加以保存作为下一次相加用,周而复始直到加法器出现溢出。

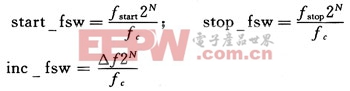

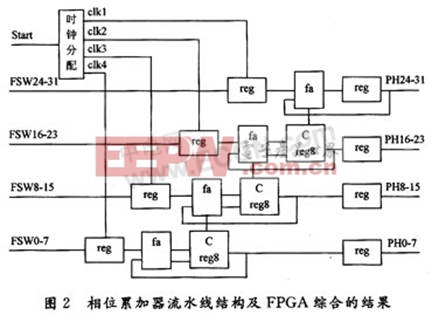

在研究过程中,取相位累加器的输出位数是32位,而对于“一次多位”的加法器来讲,最长的延迟来自进位的脉冲通过所有阶段的时候。目前已经采取了许多技术来缩短这一进位延迟,由于在老一代FPGA中没有提供内部快速进位逻辑,可以通过跳跃进位、先行进位和进位选择加法器来提高加法运算的速度,但是在现代FPGA系列中都具有特别快的“脉冲进位逻辑”,所以本设计采用进位流水线技术,这样不但提高了累加器的运算速度,而且降低了设计复杂度。流水线技术是将一个算术操作分解成一些基本操作以达到提高工作速度的一种技术,因此流水线加法器可以作为提高加法器速度的首选。本设计将32位累加器分成4条流水线,每条流水线完成8位的加法运算,流水线的进位进行级联。采用流水线结构可以提高器件的运算速度。

由于频率控制字只在频率控制字更新后的前4个周期变化,以后各个周期不再变化。基于这种情况,可以对累加器进行改进,从而节省部分存储器。改进的流水线的结构图及在FPGA中综合结果如图2所示。

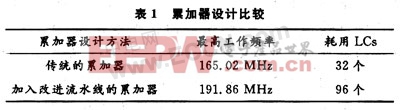

当频率控制字开始变化时,DDS控制器发送控制信号Start,开始输出控制信号,第一个时钟上升沿到来,将clk1置高,频率控制字FSW的低8位写入第一级流水线的寄存器,第二个时钟上升沿到来,写入FSW的次低8位,以此类推,第四个时钟周期上升沿到来,完成数据输入。在以后的周期内,这些数据将保持不变,直至下一次数据刷新。所以,此流水线设计不仅提高了速度,而且相对减少了寄存器的数量。在EP2C20中实现累加器,采用流水线累加器与传统的累加器速度和资源比较如表1所示。

仿真结果表明,采用进位级联的流水线技术,既能保证较高的资源利用率,又大幅度提高了系统性能和速度。

2.3 ROM压缩算法

在设计中为节省ROM的空间,尽量节省芯片资源,通常累加器的寄存器输出只有其高K位被用于频率合成,其余的较低的N-K位则舍弃不用,这就是所谓的相位截断。在实际应用中,还希望进一步节约ROM的占用,而ROM压缩最简单的方法是利用正弦信号的对称性,利用一个象限的信号通过地址变换来表示全部的正弦信号。

电机保护器相关文章:电机保护器原理

评论