10G信号抖动测量的检定分析

由于不断追求更高性能,有效数据窗的单位间隔(UI)继续缩短。速率为1Gbps时,UI为1000 ps;5Gbps缩短为200ps;10Gbps则为100ps。对于100ps的有效数据窗,在系统没有连贯而可靠地发送和接收数据之前,只能容忍很小的Tj (总抖动)。以上述速度传输时,Tj结果需远小于100ps,而Rj (随机抖动)更是以飞秒(fs)为单位。有什么技术和工具能用来检定这些飞秒系统呢?

本文引用地址:http://www.amcfsurvey.com/article/195260.htm基本上,随着速度的提升,高速I/O设计遭遇到较以往更大的挑战。很多最新标准要求物理层的比特误码率为10–12。然而,随着UI逐渐缩小,要想保持这个数量级的误码率也越来越难。最终,这就意味着设备级抖动要继续缩短。例如,5Gbps的SuperSpeed USB 3.0规定Rj为2.42ps RMS;10Gbps的SFP规定Tj为28ps,Rj为1ps左右。

定时分析

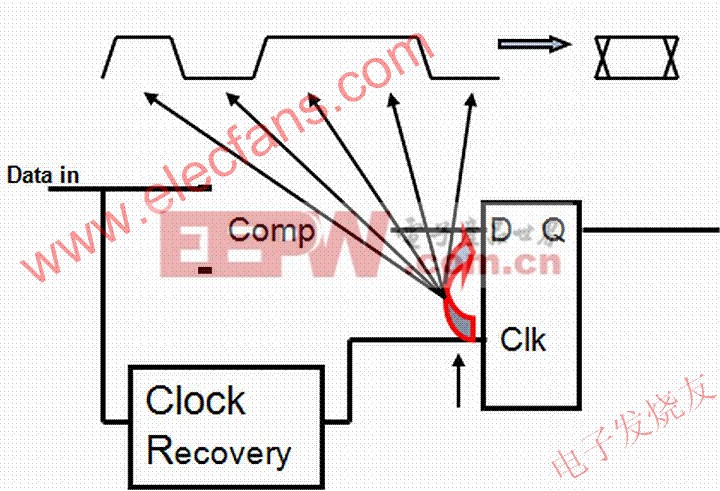

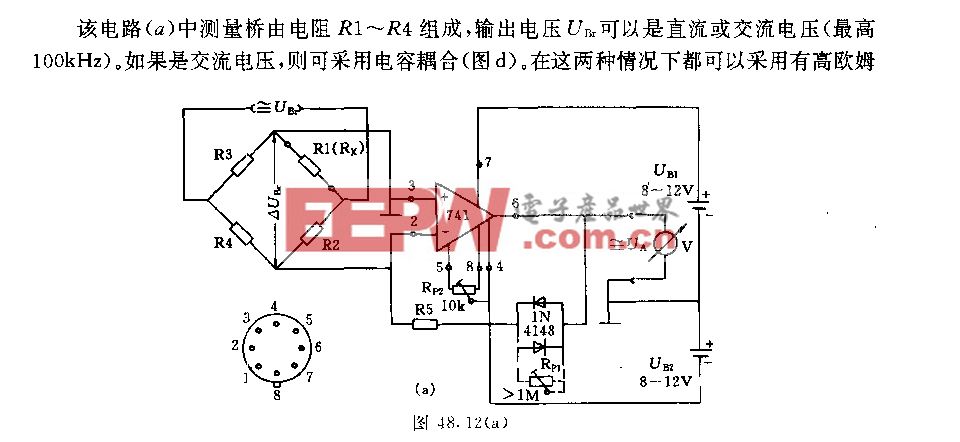

所有采用电压变换来体现定时情况的电气系统,都伴有讨厌的定时抖动。当信号速率不断提高、电压摆动缩小以降低功耗时,系统的抖动在信号发送间隔占到相当大的比重。这种情况下,抖动成为基本的性能限制。是否具有抖动检定能力,对成功运用符合性能要求的高速第三代(Gen 3)系统至关重要。如图1所示,每个时钟的数据级、上升沿和下降沿都在D处表示出来。数据锁存是数据通信的关键环节,无论在何种工具(示波器或软件仿真系统)上,都以眼图形式显示。在每个时钟上,边沿的定时位置(如果有的话)有助于时钟/数据延时统计分布。这种位移即抖动或时间间隔误差(TIE)。

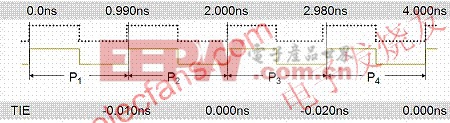

TIE抖动是相对已知或已恢复时钟测量出的信号定时误差。在串行数据的应用中,TIE通常被称为抖动。TIE很重要,因为其甚至能显示一段时间内少量抖动的累积效应。以图2为例,每毫微秒时钟边沿的TIE标准偏差是9.6ps。

图1: 串行数据中的抖动,每个时钟的数据级、上升沿和下降沿都在D处表示出来。数据锁存是数据通信的关键环节,在示波器上以眼图形式显示。

图2: TIE抖动测量有其他方法测量单波形抖动,包括周期性抖动和cycle-to-cycle抖动。

然而,测量信号波形上抖动的方法还包括测量周期抖动(period jitter)和相邻周期间抖动(cycle-to-cycle jitter)。周期抖动是对信号的测量,通常针对从一个沿到另一相似沿的重复信号。常见的周期测量工具,会测量某一信号的上升沿到下一上升沿之间的数值。采用数据传输方式(如DDR内存),同时利用上升沿和下降沿来记时数据比特,这时测量周期仅为半个周期。在采集周期测量值的有效样值后,可分辨标准偏差和峰值。该统计数据即信号中的周期性抖动。

对于相邻周期间抖动,通过应用简单算法计算刚刚获取的周期测量值。如果已知两个相邻周期的定时信息,其差值便是相邻周期间变化:周期1减去周期2。此外,对周期进行有效采样,并测量周期间的差值后,即可得出标准偏差和峰值。统计出的数据即相邻周期间抖动。

抖动分量

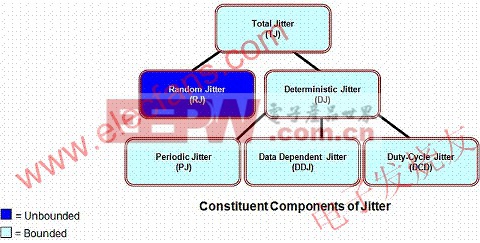

将抖动按组成进行拆分,可提高精度并看清BER性能的根源。最常用的抖动模型基于图3所示的分级结构。虽然也有分析抖动的其他方法,但这种方法是T11 FC-MJSQ所认可,且目前最为常用的,因为它直接显示与BER性能相关的分量。

图3: 按抖动类型进行的抖动分析

在这种分级结构中,首先将总抖动分为两类:随机抖动和确定性抖动(Dj),然后再将确定性抖动分为若干类:周期抖动(Pj,有时也称正弦波抖动或Sj )、占空比抖动(DCD)以及数据相关抖动(DDj,也称符号间干扰ISI)。有时也会加入另外一个类别,即有界不相关抖动BUj。

如果要测量在高信号速率时构成Tj的各分量,应采用本底噪声低、频率响应平稳、抖动测量底限低和触发抖动小的仪器。例如,ON Semiconductor发现在检定其高速ECL器件时,需采用系统抖动200fs RMS而且带宽较宽的仪器。芯片设计者发现几个ps的信号移位,甚至是在fs范围内的移位,也可能干扰发送(TX)和接收(RX)性能。

值得注意的是,尽管大多数串行通信标准都对抖动容差或抖动限值做出规定,但其中所采用的技术参数较为模糊,或者在分析抖动时采用了不同的基本原理。标准文件倾向于概述可量化的抖动限值,但并没有提出多少指导意见来帮助确定在特定应用时哪一种限值更为重要。各种形式的抖动都有可能干扰系统BER,不同的工具在检测抖动时有不同的优势。

接地电阻相关文章:接地电阻测试方法

评论