3D封装材料技术及其优点

随着移动电话等电子器件的不断飞速增长,这些器件中安装在有限衬底面积上的半导体封装也逐渐变小变薄。3D封装对减少装配面积非常有效。此外,系统级封装(SiP)技术(将二个或多个芯片安装在一个封装件中)对于提高处理速度和改善功耗的作用显着(图1)。为满足这一要求,不仅是每一种封装材料的特性非常重要,而且这些材料的组合也变得很重要。

本文引用地址:http://www.amcfsurvey.com/article/194540.htm

本文重点介绍了材料、材料设计技术以及二者的结合,例如多芯片叠层封装、用于堆叠封装的环氧模塑料和衬底以及用于先进倒装芯片封装的底充胶材料。

3D封装用的先进材料技术

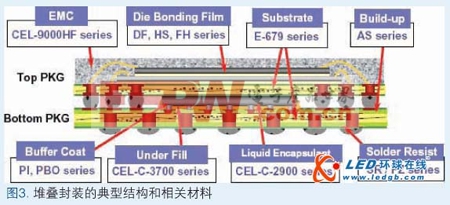

先进封装(包括3D封装)将用到各种不同的材料。例如前道材料中的低K材料、缓冲涂层和CMP研磨料,后道材料中的芯片键合膜、浆料、环氧模塑料、液态模封材料、衬底、阻焊剂等等。采用这些材料可以制作各种各样的先进封装。

用于多芯片叠层封装的芯片键合膜

存储器件广泛关注多芯片叠层封装能否实现性能更高、体积更小且更薄。图2(上)示出了多芯片叠层封装的典型结构和发展趋势。此时,芯片键合膜(DAF)的性质对提高封装性能极为重要。晶圆厚度与日俱减,堆叠芯片的数目则不断增加。由此产生了下列问题(图2下):DAF层压DAF后薄晶圆的翘曲;将芯片粘到衬底后封装的翘曲;热循环测试过程中的分层和芯片破裂。

为了解决这些问题,研发了用于DAF的新颖聚合物合金系统。这一材料的弹性模量低,抗热性能好,能有效地减少叠层CSP的翘曲和热应力。

堆叠封装(PoP)用的环氧模塑料和衬底

PoP是堆积一个或多个芯片封装的安装形式。一般说来,PoP是将存储器封装堆叠在逻辑封装之上,以节省PCB空间。由于在PoP中的总封装高度增加了,必须尽可能减薄衬底和模塑材料的厚度(图3)。较薄封装的麻烦之处是PoP的连接问题,这一点在顶层封装和底层封装的翘曲程度不一样时尤为严重。所以,控制或减少每一封装的翘曲很重要。由于衬底、环氧模塑料(EMC)和底充胶材料(UF)的热膨胀性质直接影响封装的翘曲,因此,调整这些材料的性质比过去更为重要。

衬底和EMC的热膨胀系数(CTE)对封装的翘曲有直接影响。用新树脂系材料可以开发出适合于薄封装的低热膨胀系数衬底和高热膨胀系数EMC.

先进倒装芯片封装用的底充胶材料

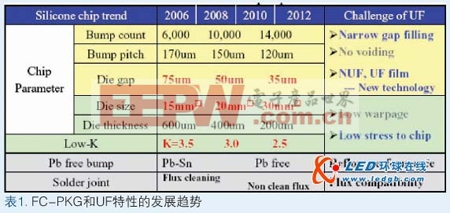

如表1所示,倒装芯片封装的发展趋势是密度更高、芯片与衬底间间隙更窄、芯片尺寸更大、速度更快(更低k值)。低应力和窄间隙填充将来对底充胶材料越来越重要。另外,对超窄间隙封装和硅通孔(TSV)封装来说,迫切需要像不流动的底充胶材料和底充胶膜等预涂材料。正在开发满足这一需求的新颖高强度树脂系材料,这些材料对减少低k大芯片的破裂很有用。最新开发的底充胶膜特别适用于减少一些综合工艺步骤。

评论