集成在半导体测试中的重要性

在今年5月1日于美国加利福尼亚州伯克利(Berkeley)举行的2006年VLSI测试研讨会上,一个专家小组探究了可测试设计(DFT)的发展前景。我们的姊妹出版物EDN的执行主编Ron Wilson报道说,讨论的主要问题是单点工具或集成DFT是否最佳(参考文献1)。参加讨论的专家所代表的公司包括Cadence Design Systems、Mentor Graphics、Synopsys、SynTest和Virage Logic,他们一致认为:如欲建立DFT与设计工具、诊断工具、可制造性设计工具和ATE的联系,那么集成将是不可或缺的。

本文引用地址:http://www.amcfsurvey.com/article/193894.htm据Wilson报道,与会专家Sanjiv Taneja(Cadence公司负责Encounter Test产品线的副总裁)发表意见说:EDA行业是以一批单点工具起步的,而如今这些单点工具已经发展到了适合一种“包容型”架构(all-encompassing architecture)的水准。

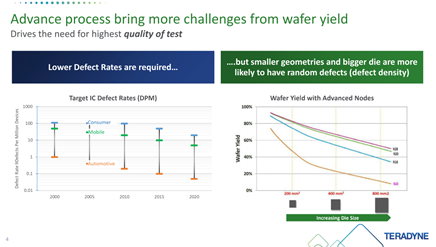

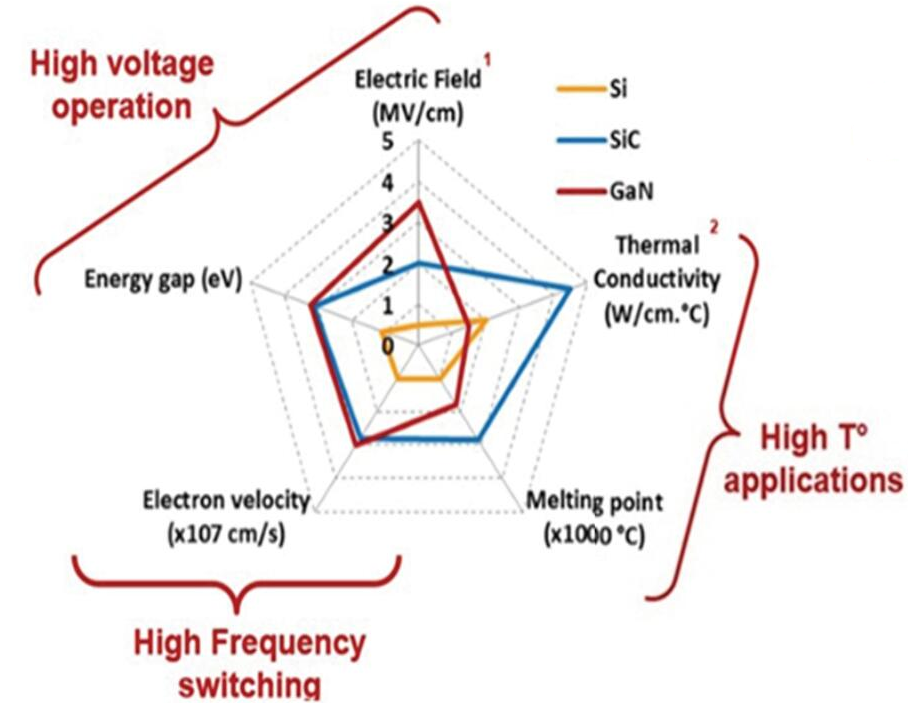

构筑一个用于解决设计、测试和成品率问题的包容型架构是Magma Design Automation公司的目标。该公司旨在利用其Talus平台来实现采用65nm及更小工艺几何尺寸制造的IC的快速设计,这被该公司描述为一个从RTL至输出设计数据带的“光刻实施流程”(lithography-aware implementation flow)。据Magma公司的一位高级市场主管Behrooz Zahiri称,目前推出的是β版的Talus平台,用于解决定时、区域、功耗、信号完整性、DFT和可制造性方面的问题。

当我向Zahiri问起该技术的有关情况时,他告诉我:Talus的主要特点之一是自动化程度有所提高。他把以往的EDA方法描述为“电子设计辅助”,为了把DFT、内置自检(BIST)、线负载建模、平面规划以及有可能以单点工具的形式存在的其他功能连接在一起,需要进行大量的脚本设计及其他的工作。他说:这样的人工方法已呈难以为继之势,因为每项设计的投资金额将有可能从130nm工艺节点时的500万美元攀升到45nm节点时的5000万美元。

Zahiri说:最初将提供两种版本的Talus,即:Talus LX和PX,它们分别面向逻辑和结构设计。他说:将针对可制造性和成品率学习进一步强化Talus。他表示,更多的细节信息在7月24日至28日于美国加利福尼亚州旧金山举行的设计自动化会议上公布于众。

不过,尽管有人在努力地把设计、测试和成品率控制组合成单一流程,但是,其他的替代方案也在接连面市。例如:Stratosphere Solutions公司刚刚首度推出了其StratoPro平台,按照该公司首席战略主管Prashant Maniar的说法,这个平台是旨在“构建符合集中化市场需求的独创技术”的工作成果的一部分,在此场合中,它抑制了由参量可变性所导致的成品率下降。另外,Incentia Design Systems公司最近公布了其TimeCraft软件的一个新版本,该软件是专为改善面向90nm和65nm设计的静态时序分析的准确度和效率而设计的。

归根结底,集成化的潮流是不可逆转的,但是,旨在解决前沿工艺中出现的各种问题的新型工具同样也会不断涌现。

评论