解决多总线系统级芯片测试问题的多域方法

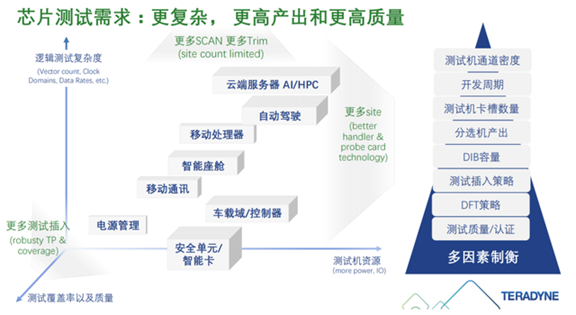

多总线IC设计的迅速涌现将使测试过程更为复杂,对于基于多时钟域和高速总线的复杂IC设计,传统的ATE方法缺乏必要的多域支持和足够的性能以确保快速的 测试开发和高效能。本文提出在测试复杂的多域IC过程中,可以使用单周期和多周期模式策略。通过将适用的模式策略与在这些平台中有效使用的高级ATE工具 相结合,测试工程人员可为高性能IC(如北桥)设计更有效的测试解决方案。

本文引用地址:http://www.amcfsurvey.com/article/193867.htm随着数据率的增加,自动测试仪器(ATE)通常会 丧失时序灵活性。在不支持多时域的ATE系统中,必须进行必要的折衷:要么运行在较低的数据率上,要么通过改变仿真以使其中一个时钟域工作在与现有时域相 同的数据率上。上述两种情形中,器件将不能以与“原始模式(native mode)”激励相同的数据率进行测试。

为了测试 这些多时钟域总线及更新的异步串行总线,工程人员需要尽可能接近待测器件的测试系统,因为测试系统将用于终端应用,这被称为“原始模式”测试。原始模式下 的测试可以改进整体故障覆盖率和故障诊断,因为设计人员可以随意改变任何一条总线,而其余总线仍能在期望的速率下运行。具有这项功能同样也能改进测试时 间,因为无需载入或改变设定的时间,而且测试模式/时序也更容易开发。

现在,高级器件(如个人计算机系统中使用的北桥和南桥芯片组设备)可以包含两个以上时钟域,而数据率高达400Mbps的高速串行总线则加重了系统复杂度。北桥和南桥是传统个人计算机架构中的两个核心器件。 南桥处理系统的I/O功能,而北桥则负责系统处理器、图像子系统、内存和PCI夹层总线之间的高速通信。

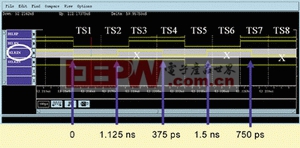

与早期的器件不同,像北桥这样的精密IC具有完全独立的高速总线,这要求测试支持独立的周期长度及带有独立循环和配对循环的时间设定。例如,北桥部分具有4 个独立的功能域,并且在不同的测试中,这些域也将形成不同的组合。某个测试可能具有运行于400Mbps的DDR和AGP组合,而CPU总线和南桥链接则 运行于533Mbps。几毫秒之后,另一测试要求DDR总线工作于另一不同速率。那些只支持双时域的测试器将无法满足这样的灵活性要求。在一种情形下, 3.0ns周期域将会导致问题(如图1所示),因为该周期域下的时序在时间设定交换中将强置为1.875 ns的时序周期;而在另一情形下,测试工程人员可将器件的测试模式拆分为两组:3.0 ns域和1.875ns域,而且完全可以同时运行这两种模式,但两种模式必须具有不同的时间基点。

图2中的示例只是测试中需要支持的各种总线-速率关系中的一种。这些总线可根据不同的测试改变速率关系:在一些测试中,一条总线的速率可以唯一确定;而在其他测试中,一些总线或许将出现问题,从而使新总线进入多时域模式。

尽管早期的ATE架构通常只支持单个高速时序发生器,而其他的测试系统(如Credence公司推出的测试系统)则早在十几年前就开始支持4个或更多的时 域。通过采用现代先进的多时域测试系统(如Octet)中的工具和特性,测试工程人员可设计具有成本效益的测试过程,这些过程可以满足先进多时域IC不断 增加的测试需求。

测试开发

为了处理具有这种复杂度的器件,测试开发必须广泛了解待测设备(DUT)的基本信息。通常,复杂器件往往未获取充分的设计数据就送达测试部门,因此测试工程人员不得不利用“逆向工程”获取所需的数据。

以前,测试工程人员只需知道电源和接地的位置、I/O配置就能路由至任意引脚。随着更快总线器件的涌现,工程人员意识到现在他们必须将专门管理这些高速总线 的测试器资源作为下一步研究对象。在不久的将来,PCI快速总线和其他资源同步总线(SSB)将能被专用的测试器信道资源使用,从而支持传统的数字测试功 能及新的SSB测试功能,如抖动插入/检测、伪随机比特流(PRBS)生成与捕获以及时钟恢复功能。

随着器件速率和复杂度的增加,测试工程人员将需要更详细的DUT数据,以构建适当的测试器件和过程。如果这些设备的数据率超过几百兆bps,那么测试设置就变得尤为重要,因此需要重点关注器件设计。工程人员必须确保差分对布线在长度和阻抗上匹配,并采用高质量器件。

过去,在器件开发中可以吸收DUT开发经验。现在,对DUT的理解已远比开发重要。通过将提供的数据同公布的标准进行比较,测试工程人员可以在总体上更好地理解DUT操作及特定的时钟域。获得了上述信息,测试工程组可以确定如下关键特性:

独立域数目

每个域的最大频率

每个域的引脚数目

最小电压波动

差分信号

终止

多域测试方法

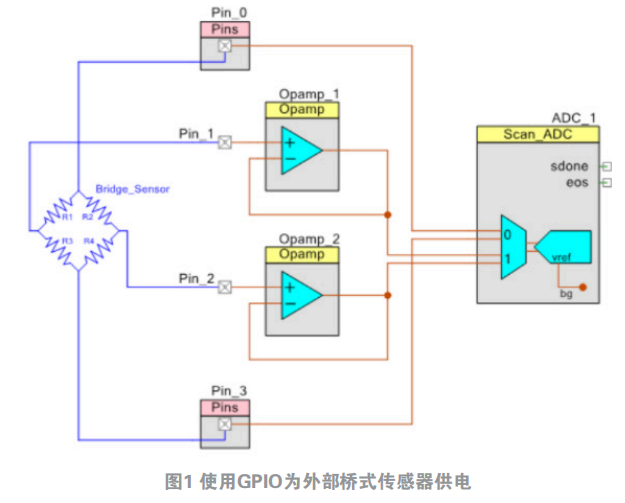

如图2所示,北桥部分具有多路总线,但只需要有限个独立的时钟域用于测试。这些总线通过内部PLL进行计时,该PPL的参考时钟通常工作在很低的频率上。前 端总线(FSB)时钟的频率为133MHz,而数据的频率则是其四倍。在AGP时钟频率为66MHz的情形中,内部PLL可以将该频率提升8倍,达到 533MHz。术语“4倍频”则能以另一种方式指示数据由频率是主时钟数倍的内部时钟进行计时。

尽管众多不同的时钟处于北桥 的一个域中,但DCLKIN引脚(内存时钟)并不同支持其余时钟的测试器周期完全对齐。为了处理这种非对齐波形,带有时间设定支持的测试器可在连续的方向 上提供不同的边缘器件。例如,测试模式生成软件可生成具有8项时间设置的重复模式,这些时间设置可在测试器上重复生成。

总体而言,测试工程人员可采用以下两种常用解决方案(单时域或多时域)中的一种解决时钟域问题:

单时域:测试模式采用时间设置重生成域关系,该方法可能用尽目标ATE上的时间设置/边缘设置内存。

多时域:仿真数据将拆分为具有独立时序的多个ATE模式,该方法依赖于器件设计。

当启动首个多域项目时,如果ATE系统支持,那么理想的方法是在特定的模式上实现这两种方法。这种方法可以使测试工程人员在调试期间获取更多的灵活性。

将模式转换为特定测试器周期边界的过程称为“周期化”。典型的测试向量生成工具默认状态下将尝试生成单时域模式,但许多早期的ATE平台具有受限的时间设置 资源,而且一些模式完全不适合或者需要在较低的频率上运行。实现多个测试器周期则更为困难,但测试工程人员可在不同的速率条件下为实现“周期化”以进行 I/O子集处理。测试中,载入不同的模式集并在ATE上作为独立实体运行。如果混淆了引脚顺序,那么将很难区分属于不同时钟域的引脚。这时,脚本就是对现 有专用于检查的模式文档中的总线进行分组的最有效工具。不同的ATE对于所能支持的域数目及每组中引脚的数目具有不同的限制。因此,测试工程人员在设计测 试架构之前,充分了解域的需求至关重要。

小结

除了DUT特性,测试工程人员还必 须充分了解目标测试器的性能,以有效地采用多域测试方法。除了支持的时域数目,工程人员还需要了解支持的时间设置数目和任何高速率限制。这时物理学原理也 同样适用,而且许多工程人员还试图理解任何平台上I/O频率超过150MHz条件下的聚焦标准和往返时延。

评论