使用新型 Virtex FPGA 开发小型软件无线电平台:S

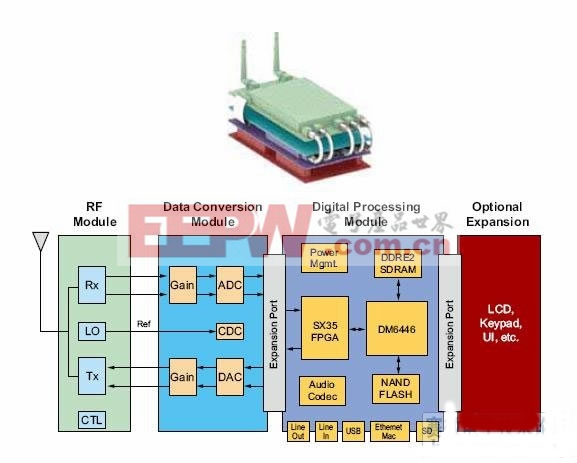

SFF SDR(小型软件定义无线电)开发平台是一种模块化的 RF/IF/基带平台(图 1 和图 2)。该平台展示了 Xilinx 和德州仪器 (Texas Instruments, TI) 的最新芯片产品以及最新高级设计流程和软件架构。 这个平台还为手持设备开发人员提供了特定的关键功能,如实时功耗配置和监测。

本文引用地址:http://www.amcfsurvey.com/article/193341.htm

此平台是德州仪器、Xilinx 和 Lyrtech 以及众多主要软件工具供应商联合开发的成果。 此平台具有一个 Xilinx® Virtex-4 器件,该器件的先进功能可为您开发高效的功耗优化设计助一臂之力。

本文将讨论组合 DSP/FPGA 架构和设计的趋势及其在 SFF SDR 开发平台中体现的方法。 本文还将介绍用混合设计流程(对于 FPGA 使用基于模型的开发方法,对于片上系统的 DSP 使用 C/汇编语言)设计的简单的家用无线电服务 (FRS) FM 调制方法和较复杂的 GSM 调制方法。

图 2 – SFF SDR 开发平台的框图与技术

SFF SDR 开发平台

SFF SDR 开发平台提供从天线到基带处理的完整信号链。 可以用这套系统为军事、公安和商业应用创建单协议或多协议无线电手持设备。 这套系统还可用作快速原型设计和测试平台。 另外,该平台为了与 The MathWorks 的 Simulink 基于模型的设计 (MBD) 工具一起使用而进行了集成,所以可以选择使用 C/HDL 或 MATLAB Simulink 快速测试概念验证设计以及对架构进行成本和功耗优化。

与市场上其他 SDR 开发产品不同,SDR 开发平台是软硬件共同开发环境,可为多协议 SDR 设备提供全套构件,包括 RF 前端模块、模数及数模数据转换模块和数字处理模块。 通过将基带、IF 和 RF 分割成分立模块而非采用单一混合架构,就可以用替换己方或第三方模块的方法增强您的无线电开发能力,并进行成本和功耗优化。 这一灵活性至关重要,因为它使您有能力针对日新月异的行业要求调整自己的产品。

基带模块具有一个 Xilinx Virtex-4 SX35 FPGA 和一个 TI TMS320DM6446 芯片。 TI 芯片包含一个 TMS320CC64x+ DSP 内核和一个 ARM9 通用处理器内核。 SDR 开发平台具有一个独特的功耗测量 API。 此 API 可测量 FPGA、DSP 和 ARM 的加载并报告实时功耗数据。 这样,您就可以提取特定数据速率下的突发和峰值功耗等重要信息,从而准确地估计电池寿命。 您还可以快速估计不同系统配置的功耗影响。 例如,您可以尝试在 FPGA 和 DSP 之间进行不同的系统功能分配,以获得最佳的功耗/性能平衡。

FRS 和 GSM 应用示例

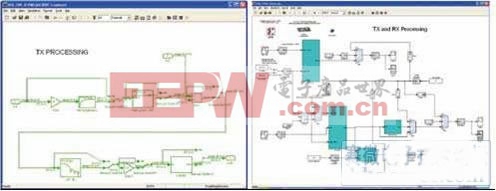

SFF SDR 开发平台包含一个基本应用示例: 简单的 FRS FM 波形。 图 3 所示示例完全采用基于模型的方法设计,以便显示该平台的快速原型设计功能。 此应用还说明了如何在 DSP 和 FPGA 之间分配应用功能,并且说明了将不同处理部分从 FPGA “转移”到 DSP(以及相反过程)的效果。

( a) (b)

图 3 – 用“完全基于模型设计”的方法设计简单的 FRS 波形。 图 3(a) 所示为 DSP 处理(Tx 端);图 3(b) 所示为 FPGA 处理(Rx 和 Tx 端)。

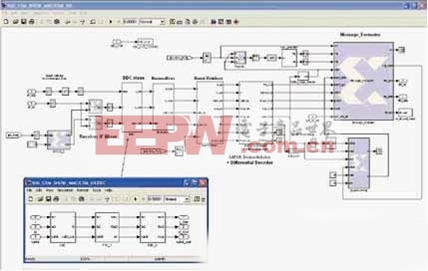

图 4 所示为使用 Simulink/Xilinx System Generator for DSP 中基于模型的方法实现的 GSM 物理层的 FPGA 部分。 此模型实际上是一个可执行的框图,其中所有信号处理功能都可以通过结合 Simulink 信号源、信道仿真、输出示波器和数据误码率分析进行仿真和验证。

这一方法的优点是,一旦完成仿真,即可将模型综合到 FPGA 比特流中去用实际信号执行。

我们先浅释开发过程,然后对非常具体的 DSP 相关实现和时序实现方面进行较深入的探讨。

该 GSM 项目当初的目标器件是 Virtex-II 系列,用一个 Virtex-4 器件对同样的 System Generator 模块进行了重新综合和重新验证。 可见采用基于模型的方法的最主要好处就是 便于器件重定向。

图 4 – GSM 物理层的 FPGA 模型

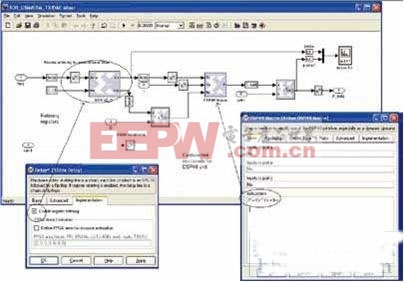

这种重定向的实现方法尚可通过第一关,但是,使用 Virtex-4 FPGA 中 DSP48 处理单元的更高级功能是为了优化设计,因为优化设计越多功耗就越小。 图 5 所示为模型的一个关键的高速部件——发送端 IF 混频器,其运行速度是 I

F 采集速度 (104 MHz)。 优化这一部分是降低功耗的关键。 这是通过“调整”DSP48 微码(如图形用户界面子窗口中所示)实现的,该微码被编程为执行一个乘加指令。 这样,与 Virtex-II 器件相比,FPGA 资源就会低得多。 由于这一优化,用电量(用此平台的功耗测量功能验证)也会低许多,Virtex-4 器件的整体功耗配置也会得到改善。

图 5 还显示了 System Generator 另一个令人非常感兴趣的优化功能——重定时功能。 这一强大功能使 System Generator 可以在整条流水线的适当位置插入锁存器。 这一自动重新定时功能确实起到了简化作用,特别是对直接数字合成 (DDS) 功能等高速部分。

Virtex-4 架构和工具的使用使 GSM 物理层的实现大受裨益。 就 FPGA 的资源和功耗而言,我们用 SFF 的功耗测量功能大大优化了实现过程。 连续功耗监测等其他功能将使您能够对运算过程中的用电量进行表征,从而进一步实现处理优化。

图 5 – 使用微码自定义 DSP48 处理单元

结论

SFF SDR 开发平台为手持设备开发人员提供了非常灵活的平台。 此平台以 TI 和 Xilinx 等芯片供应商提供的高级处理器以及 The MathWorks 等主要供应商提供的软件工具为依托,为手持设备开发人员提供了一个真正的“乐高模块箱”,在不断加速、竞争激烈而又极有前途的无线设备市场中构建出先进的产品。

评论