基于FPGA的位宽可扩展多路组播复制的实现

摘 要:用VHDL语言在FPGA内部编程实现组播复制。本文介绍其实现方法,并给出了时序仿真波形。通过扩展,该设计可以支持多位宽、多路复制,因而具有较好的应用前景。

关键词:FPGA VHDL 组播复制

1概述

组播是一种数据包传输方式,当有多台主机同时成为一个数据包的接受者时,出于对带宽和CPU负担的考虑,组播成为了一种最佳选择。在T比特路由器4X2.5G线路接口模块的硬件实现中,我们需要将数据发送到不同的目的端口,而这些端口又不是所有的目的端口。根据数据携带的组播目的端口号可以实现数据的复制,这就是本文所提到的组播复制。我们用VHDL语言在FPGA内部编程将其实现。本文第2节给出用VHDL语言在FPGA内部编程实现组播复制的过程,第3节总结全文。

2实现

我们选用Altera公司Stratix GX系列EP1SGX40G FPGA芯片。Stratix GX 是Altera 系统级可编程芯片系列中的旗舰产品,把复杂的FPGA设计提升到了系统集成的新高度。Stratix GX器件具有多达20个全双工收发器通道,每个通道的速率可高达3.125Gbps,满足了高速背板和芯片间通信的需求,融合了业界最快的FPGA体系和高性能的数千兆收发器技术。另外,Stratix GX器件具有嵌入均衡电路,每个通道的功耗非常低,具有40英寸的FR4背板驱动能力。Stratix GX器件也提供了具有专用动态相位调整(DPA)电路的源同步差分信号,工作速率可高达1Gbps。

EP1SGX40G型号的FPGA具有41,250个逻辑单元(LE),20个全双工收发器通道,45个全双工源同步通道,RAM总量3Mibt,14个DSP模块;112个嵌入乘法器,8个PLL,芯片封装为1020管脚BGA封装。

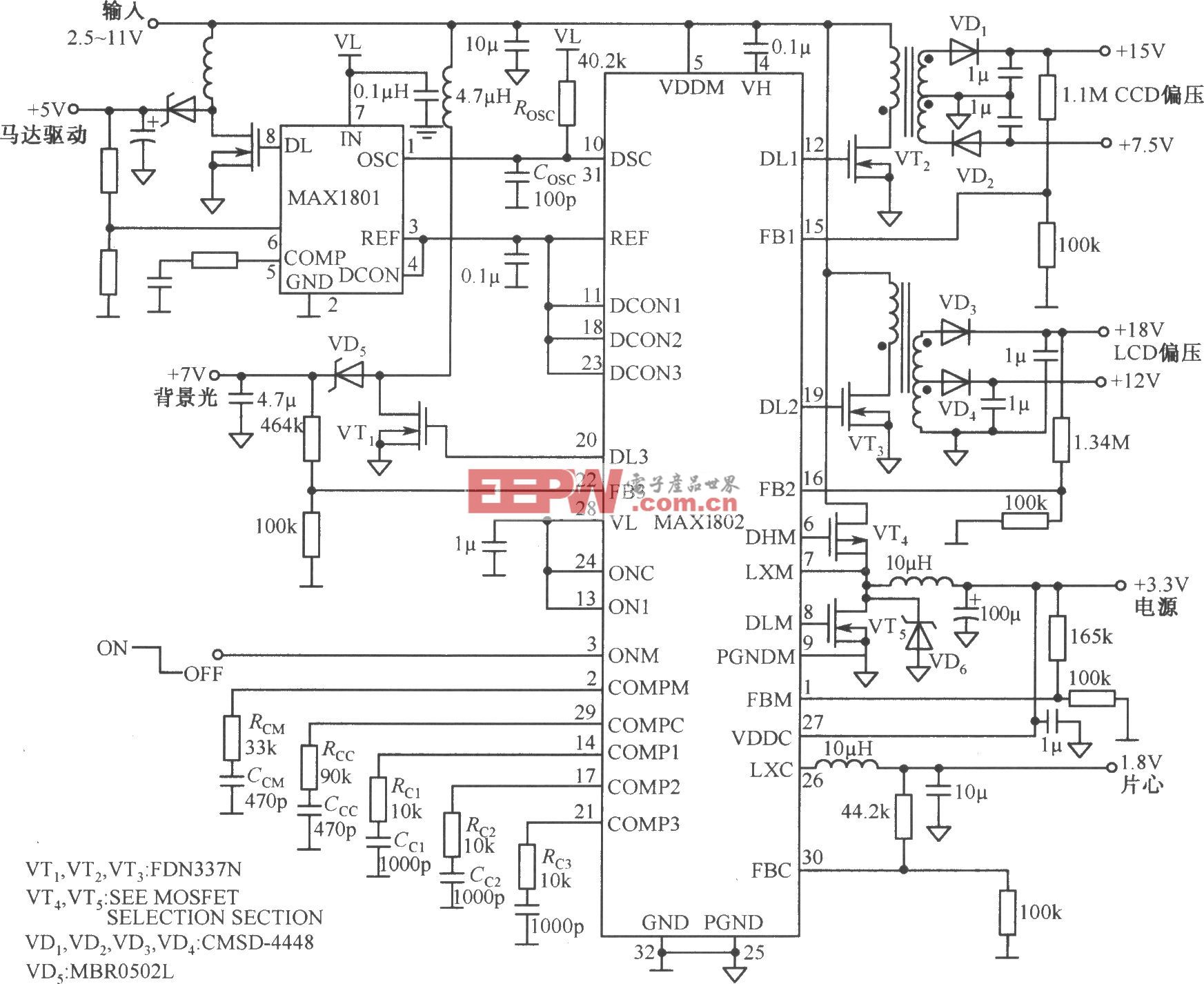

用FPGA对四路组播复制的实现原理图如图1所示。数据data_in写入4个FIFO,根据组播目的端口号选择输出。数据格式定义:data(7 downto 0)数据、data(8)包头指示(sop)、data(9)包尾指示(eop)、data(13 downto 10)组播目的端口号,13、12、11、10位分别表示a、b、c、d端口,高有效。主要程序如下:

图1 四路组播复制实现原理图

2.1.实体说明

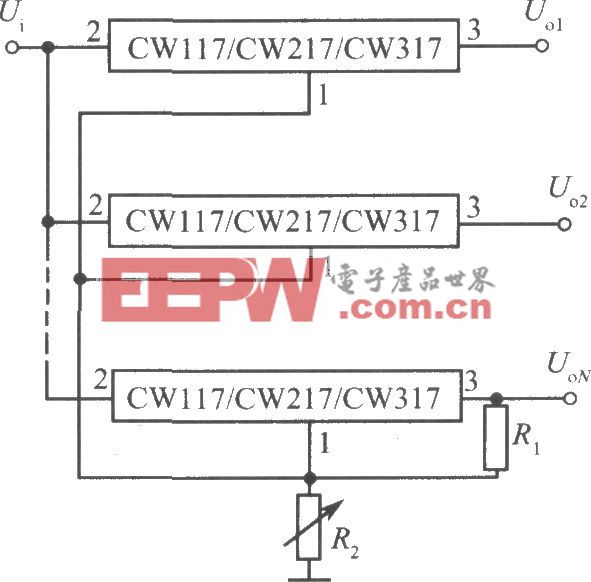

该程序已在ALTERA公司的quartusII4.1环境下用VHDL编程实现,其仿真波形如图2所示。

图2 组播复制时序仿真图

3 结束语

根据组播目的端口号,用VHDL语言对FPGA内部编程实现四路组播复制。仿真结果显示,该程序完全符合设计要求。通过扩展,该设计可以应用于多路组播复制,同时,我们也可以容易地扩展数据的位宽,因而该设计具有较好的应用前景。

参考文献:

1 S19202CBI30 GANGES Product Specification.AMCC公司,2002

2 Stratix Device Handbook. Altera公司,2004

3 边计年,薛宏熙.用VHDL设计电子线路[M].北京:清华大学出版社,2000

评论