基于CPLD的并口数据的采集和存储

摘 要:提出了一种利用CPLD实现雷达并口数据的采集和存储的方案。采用单片CPLD完成了以往需要大量外围器件来完成的雷达并口数据收发及存储功能,有效地减少了印制板上功能模块的面积,减少了系统体积,提高了设计效率;同时还利用CPLD中的锁相环倍频系统时钟大大提高系统采集速度。实践证明,基于CPLD的系统设计是灵活、现实且高效的。

关键词:CPLD;双口RAM;数据采集;存储

O 引 言

在雷达的控制和数据采集系统中通常采用并行数据总线方式进行控制信号传输和数据交换。在以往的设计中,大量使用中小规模集成电路及分立元件搭建总线数据采集和控制功能模块,不仅占用较大的印制板面积,而且设计工作量大,时序控制复杂,采集速度不理想。

将CPLD应用到该系统的设计中可以有效地解决上述问题。CPLD可以实现许多中小规模集成电路的功能,因此可以有效地减少印制板上功能模块的面积,同时减少系统体积。利用CPLD的在线编程和仿真功能可以模拟系统各类信号的时序,大大提高设计效率。

l 系统硬件结构

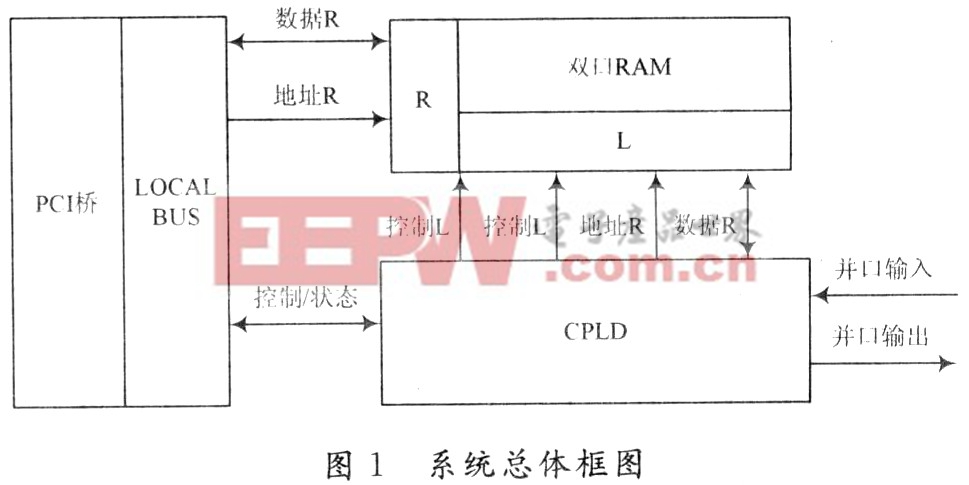

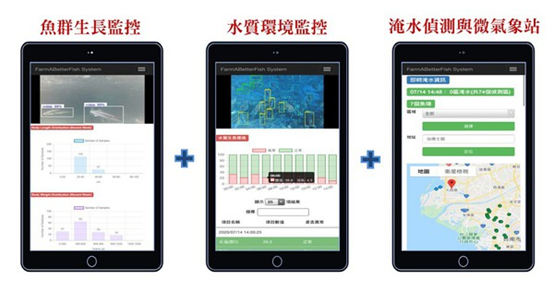

为了实现高速数据处理与数据传送,系统采用CP―CI总线接口形式。该设计方案为雷达系统提供了两路并行数据总线接口。其中一路并口由CPLD控制,将存储空间中系统已经准备好的数据发送给雷达;另一路用于接收雷达传回的回波信号,并由CPLD控制放到存储空间中去。系统设计框图如图1所示。

1.1 CPCI总线接口

CPCI总线接口兼顾了PCI总线的高速度,同时丢弃了金手指式互连方式,而改用2 mm密度的针孔连接器,提高了系统的可靠性,增强了负载能力。在工业领域已经得到广泛应用。

总线接口电路采用PLX公司的高性能接口芯片PCI9054。它采用了先进的PLX数据管道结构技术,是32 b,33 MHz的PCI总线控制器。其主要特性如下:

支持主/从两种访问方式,其峰值传输速率可达133 MB/s;提供了2个独立的可编程DMA控制器,每个通道均支持块和分散/集中的DMA方式;局部总线速率高达50 MHz,局部总线的时钟可以由外部提供,且该时钟可以与:PCI的时钟同步;内部有6种可编程的FIFO,以实现零等待突发传输及局部总线和PCI:总线之间的异步操作。

系统启动的时候,在系统配置的周期内,PCI9054从配置E2PROM中读人配置信息完成初始化。这里采用NS93CS56完成对PCI9054的初始化配置。

1.2 可编程逻辑器件

可编程逻辑器件选用ALTERA公司的EPlC3,其型号为Cyclone系列的产品,具有内部逻辑分析功能。在JTAG方式下,通过下载电缆即可观察到各个IO引脚及内部各个寄存器中的数据,调试十分方便。

1.3 存储器

本系统中采用双口RAM作为PCI总线和并口数据存储和交换的媒介。考虑到用于并口交换的数据量较大,因此选用IDT公司的64K×16 b双口芯片IDT70V28。做成乒乓方式的存储结构,以实现并行操作,节约处理时间,保证实时处理。

2 系统设计及原理

2.1 锁相环

在印制板上采用的晶体或晶振的输出频率较低,并不能满足系统需求,为了能够得到较高的采样速度,必须有一个高频率时钟作为系统时钟。EPlC3内部的锁相环功能可以对输入时钟进行倍频和降频的处理,还可以根据需要产生不同的时钟相位。倍频后的时钟可以作为CPLD内部的系统时钟使用,也可以输出至CPLD外部,作为其他器件的时钟输入。

在本系统中采用一个20 MHz的晶振作为CPLD的输入时钟,通过倍频产生一个100 MHz的时钟作为内部的系统时钟,同时产生一个33 HMz的时钟输出作为PCI9054的局部总线异步时钟。

2.2 并口数据收发

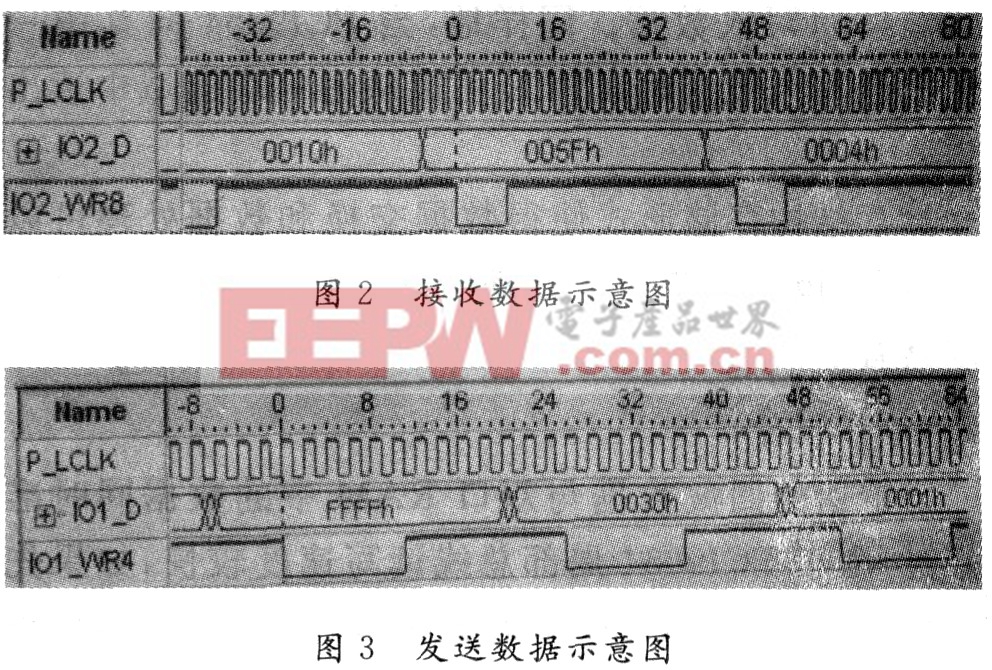

雷达回波包括16位宽度的数据和握手信号,首先需要用CPLD对握手信号进行接收和处理。接收到的、握手信号都为下降沿触发脉冲。需要注意的是,接收到的握手信号必须去除毛刺和噪声产生的干扰,避免系统接收到错误的数据。为了去除毛刺干扰产生的影响,应使低电平保持一段时间,以减少误触发。根据系统中毛刺和噪声的周期设定检测门限,例如,当握手信号经电缆传输至接口板时,有时会在前沿产生一个15~20 ns的毛刺,因此可以在检测到握手信号的下降沿后接着连续记录四个以上时钟周期的低电平信号,只有当这四个周期的信号电平全为“0”时,才确定本次握手有效。并口接收数据示意图如图2所示。

评论