多路数据采集系统中FIFo的设计

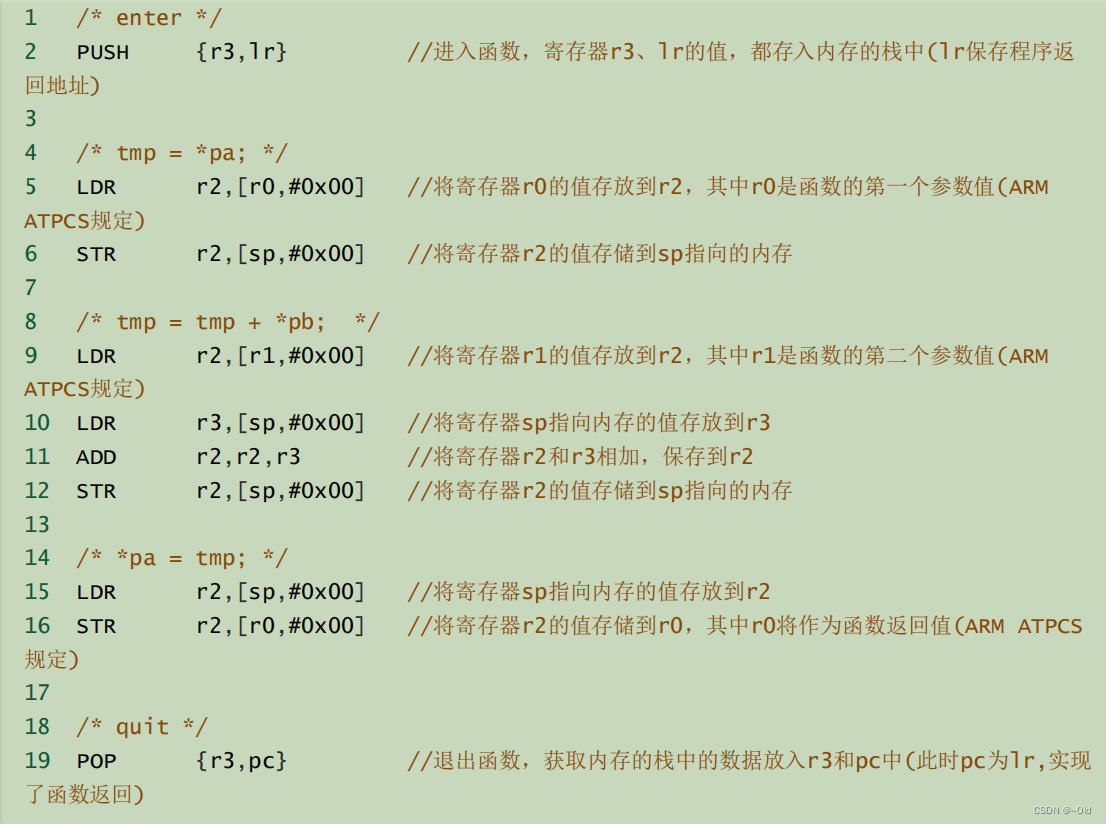

摘 要:首先介绍了多路数据采集系统的总体设计、FIFO芯片IDT7202。然后分别分析了FIFO与CPLD、AD接口的设计方法。由16位模数转换芯片AD976完成模拟量至位数字量的转换,由ATERA公司的可编程逻辑器件EPM7256A完成对数据的缓存和传输的各种时序控制以及开关量采样时序、路数判别。采用FIFO器件作为高速A/D与DSP处理器间的数据缓冲,有效地提高了处理器的工作效率。

关键词:IDT7202;CPLD;FIFO;电路设计

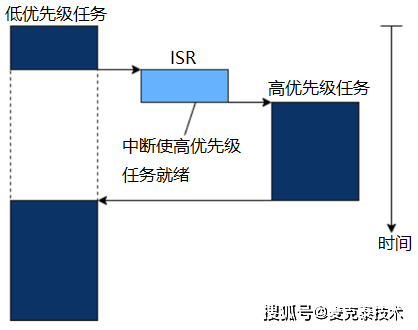

随着数字信号处理芯片DSP技术的发展,信号处理的速度越来越快,容量越来越大,为了配合不同时钟域之间的数据传输,必须使用FIFO来达到数据匹配的目的,从而提高系统性能。

1 系统的总体设计

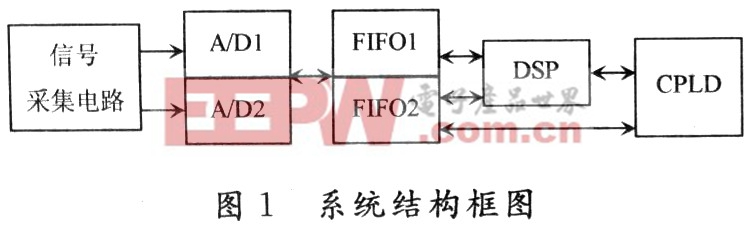

系统主要由信号采集电路AD,FIFO,CPLD和TI公司数字信号处理芯片TMS320C25409组成。可以采集32路模拟量,64路开关量。接收到的模拟信号首先要通过运放放大、采样、然后通过模拟电子开关、再实现A/D转换,转换的数据经FIFO送至DSP处理,CPLD负责控制数据采集、A/D转换和数据读写的时序。系统结构框图如图1所示。

系统中使用了2片高速A/D转换芯片AD976,AD976是AD公司生产的模数转换器,它是采用电荷重分布技术的逐次逼近型模数转换器,FIFO选用了IDT公司的IDT7202。它具有输入和输出两套数据线,独立的读/写地址指针,在读/写脉冲的控制下顺序地从双口FIFO读/写数据,读/写地址指针均从第一个存储单元开始,直到最后一个存储单元,然后又回到第一个存储单元。系统采用了2片IDT7202将数据宽度扩展为16位,DO~D1为64路开关量数据;D2~D15为32路模拟量数据。在系统工作时,IDT7202内部的仲裁电路通过对读指针和写指针的比较,相应给出FIFO的空(EF)和满(FF)状态指示;CPLD可以根据所获得的FIFO状态标志控制FIFO的读/写时序,实现对FIFO的读/写操作。

2 FIFO芯片IDT7202的介绍

FIFO(First In First Out)简单说就是指先进先出。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采集、高速数据处理、高速数据传输以及多机处理系统中得到越来越广泛的应用。IDT7202是一种高速、低功耗、双端口存储器,输入、输出有9位数据,芯片容量为lK×9 b,输入/输出端口由单独的时钟和使能信号控制,具有“空”、“满”、“半满”和“几乎空、几乎满”标志。IDT7202的9位输入/输出端口由单独的时钟和使能信号控制。输入端口由写使能信号(W)控制,当写使能W为低时,数据被连续写入FIFO存储器中。同样,输出端口由读使能信号(R)控制,而且有一个输出使能引脚(OE)。IDT7202还有一个复位端(RS),当RS为低时,IDT7202的各个标志位全部回到原始状态。

3 FIFO与CPLD的接口设计

ATERA公司的可编程逻辑器件支持多种I/O电平标准,包括3.3 V,2.5 V和1.8 v的LVTTL和LVCMOS电平。由于FIFO必须是5 V供电,所以CPLD将数据从FIFo读人内部存储器时,需要经过一个电平转换芯片。系统选用了SN74LVCl6245A具有三态输出的16位总线收发器,它支持8/16位数据的双向传输。

在FIFO与CPLD数据通信接口设计中,CPLD主要输出控制时序到IDT7202的复位、写和读端口,实现A/D转换数据到FIFO的存储,并将数据从FIFO读入CPLD的内部存储器。一旦CPLD检测到两个AD976的“BUSY”信号都为高电平,且延时满足,CPLD就使FIFO的写信号“W”输出为低电平,允许向FIFlO中写入数据。同时检测FIFO的满标志信号FF。若该信号为低,则说明FIFO已经写满,此时,CPLD输出读时序给该FIFO,向FIFO中读数据,同时检测FIFO的空标志信号EF,若该信号为低,则说明FIFO中数据已经读空,不允许读数据,除非再有数据写入后。本系统中采用两片IDT7202,它们的复位、写和读端口分别联在一起,数据同时读写。数据DO~D8从第一片输出,D9~D15从第二片输出,D16,D17空的两位数据接地。DO~D1为64路开关量数据,64路开关量数据由8片8D锁存器74LS373锁存直接送至CPLD,开关量采样时序、路数判别由CPLD来实现。

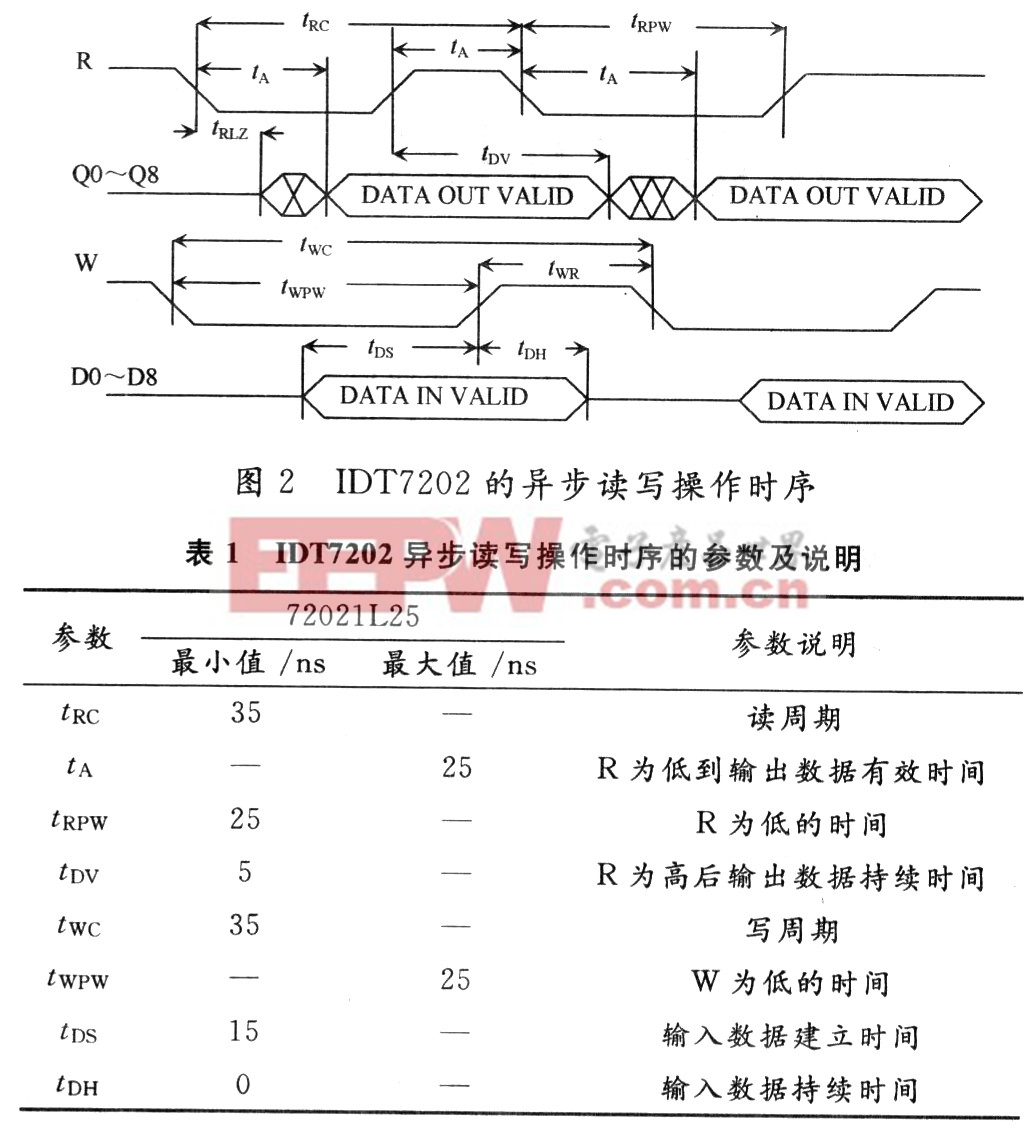

IDT7202的异步读写操作时序如图2所示,各参数说明见表1。

4 FIFO与AD976接口设计

本系统最多可接32路模拟量,需使用两片AD976芯片,转换后的16位数据分别送入两个FIFO中。当两片AD976中的任意一片中的“BUSY”信号为低电平时,进行模数转换,只有当“BUSY”为高时,数据才有可能写入至FIFO中,但数据是否写入到FIFO中,由FIFO的写使能信号来决定,当CPLD发出写使能信号有效时,转换数据才能存储到FIFO中。A/D转换数据的输出和转换时钟有一定的相位差,在CPLD内部可通过延时或时钟管理器来满足建立时间和保持时间,保证数据不失码地传输到FIFO中。FIFO与AD976均采用5 V电源,故数据线直接相连即可,为了减小外界对数据线的干扰,在数据线之间串接一个100~200 Ω的小电阻。

5 结 语

系统地介绍了一种多路数据采集系统中FIFO的设计方法。系统可以采集32路模拟量,64路开关量。系统具有抗干扰强、可靠性高、失码率低等优点。该系统可用于采集量比较多的设备中,已在电力故障监测装置中得到广泛的应用。

评论