基于CPLD的全帧型CCD图像传感器驱动系统设计

0 引 言

电荷耦合器件(Charge Coupled Devices,CCD)是20世纪70年代初发展起来的新型半导体集成光电器件。作为一种新型的MOS器件,与普通MOS器件相比,具有集成度更高、功耗更低、设计更简单、制造工序更少等优点。随着航天技术的发展,在航天器高姿态和高准确度测量、空间遥感和对地观测等领域中,性能优越的CCD相机越来越多地得到了应用。

在此,将CCD应用于数字航测相机中。数字航测相机是基于数字相机的基本原理,将图像以数字信息的形式存储、转移,并与地面实现通信。CCD图像传感器是相机的眼睛,它对相机的性能起到非常关键的作用,因此,实现电子扫描功能的CCD驱动电路是数字航测相机系统设计的关键。

DALSA公司的FTF4052M 22M Full-Frame型CCD是一款全帧型CCD图像传感器。这里在分析该器件的工作过程中,以及对驱动信号的要求后,采用了基于可编程逻辑器件(CPLD)技术,将CCD驱动电路集成在一块芯片上,实现了CCD图像传感器的驱动电路,并且结合Ahera公司的EPM7160SLC84-10完成了硬件电路的设计。

1 全帧型CCD驱动时序发生器原理

1.1 FTF4052M芯片介绍

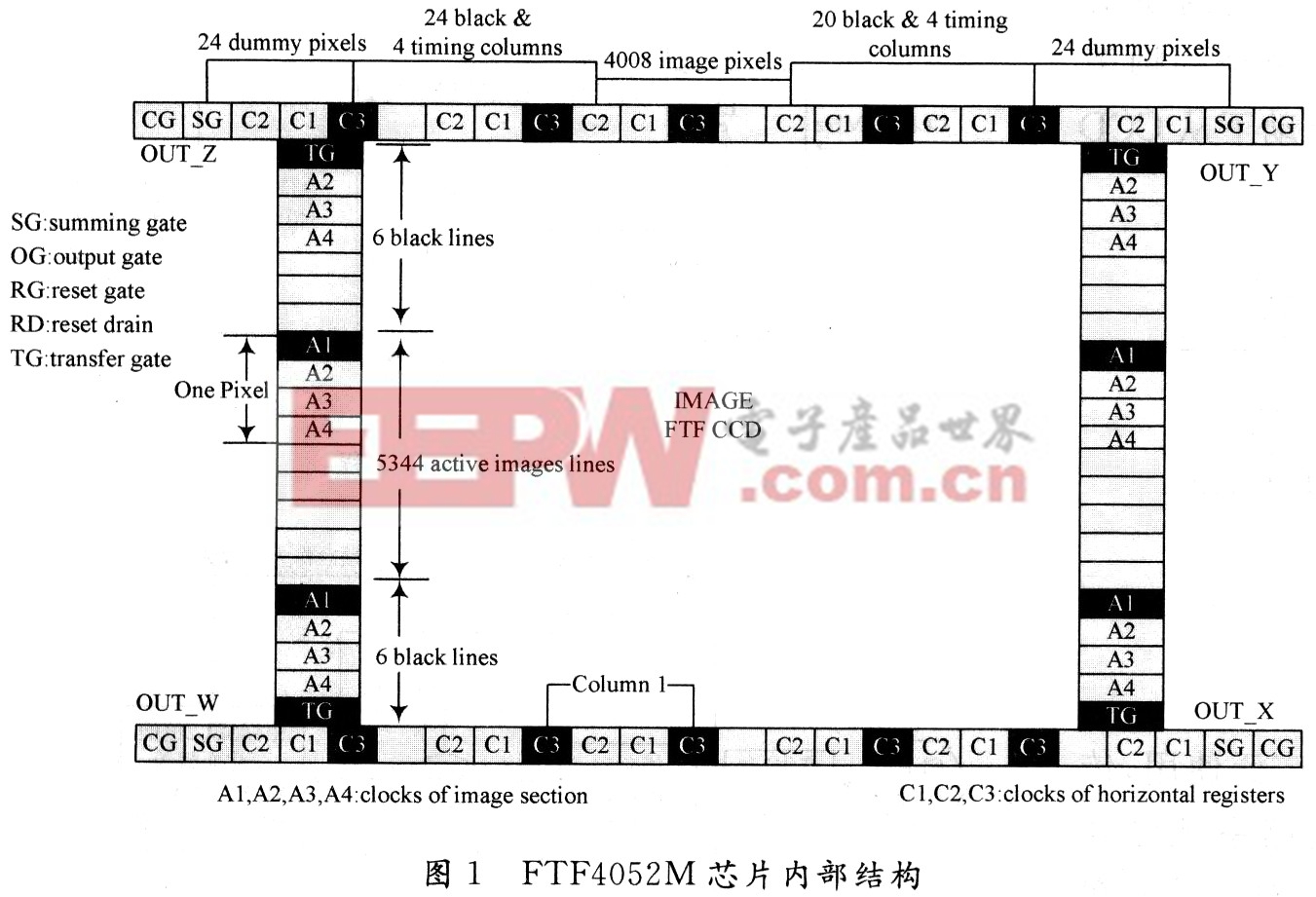

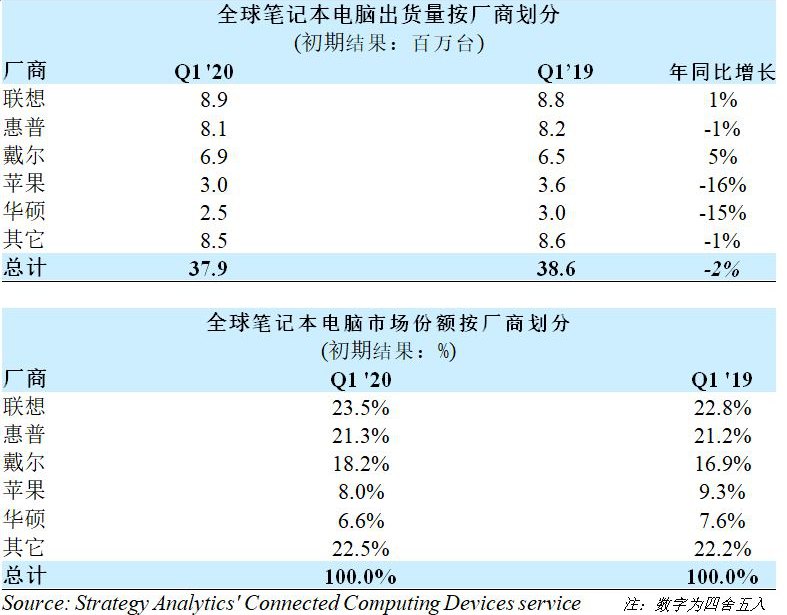

FTF4052M是22兆像素(4 008 pixel×5 334 pix-e1)的超大分辨率全帧CCD图像传感器,其内部结构如图1所示。

其主要特性如下:

(1)36 mm×48 mm的光敏面;

(2)优异的抗光晕性能;

(3)22兆有效像素(8H×5 344 V);

(4)可实现垂直子采样;

(5)高的线性动态范围(>72 dB);

(6)数据传输率高达27 MHz;

(7)可实现单路,双路和四路同时输出。

该芯片在结构上分为3部分,中间最大的区域为光敏区,即光积分区域;上下两部分为两个输出寄存器。将光积分生成的电荷水平转移到4个角的输出放大器,输出放大器将光生电荷形成的电压信号放大并转移出CCD。

C1,C2,c3为水平像素转移寄存器的时钟信号。A1,A2,A3,A4为垂直行驱动时钟信号。TG是光敏区与输出寄存器之间的隔栅;OG是输出栅;sG是输出栅之前的最后一个栅;RG是输出放大器。该芯片的最大特点是将光敏区生成的图像分成W,X,Y,Z四个对称的象限,每个象限的电荷可以以不同的方向转移,通过四个输出端同时输出,有效地提高了帧速率,单端输出的帧速率为1帧/s,而四端同时输出就可以达到3.6帧/s。

1.2 帧转移时序分析

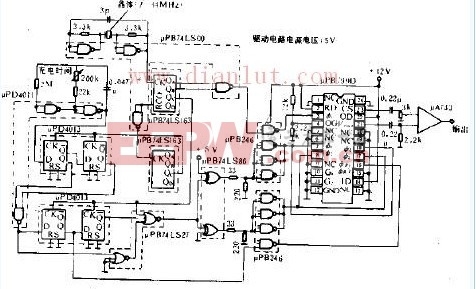

CCD的整个帧转移时序如图2所示,主要分为3个阶段,而且这三个阶段是周期进行的。在此,把空闲模式阶段定义为第一阶段,在CCD芯片空闲模式下,A时钟信号全部保持低电平。空闲模式后,CCD芯片开始进入第二阶段,即光积分阶段。

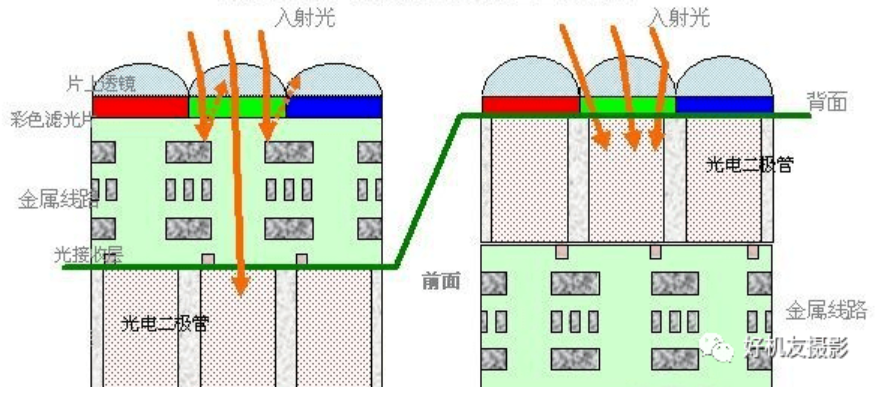

如图2所示,SSC为系统内部基准时钟信号,用于校准整个CCD的时序。VA high是控制四组A时钟的高低电平转换信号;TG信号的相位和频率与A1完全一致。由于CCD芯片FTF4052M发球全帧CCD芯片,光敏面占CCD面积的大部分,为了得到100%的污染点图像,必须加上机械快门。它的开启由Trig-in信号完成。当Trig-in信号上升沿到来时,触发快门使之进行开启动作,CcD准备进行光积分。在Trig-in信号上升沿之后,当基准时钟信号SSC的第一个上升沿到来时,产生脉冲宽度为190.6 ps的信号CR,用于对CCD进行初始化。当CR脉冲到下降沿时,快门彻底打开,ccD正式进入光积分阶段。A1继续保持低电平;A2,A3,A4上升为高电平。因为CCD芯片中的每个像素都可以看作是由四个栅极(每个栅极连接一相时钟信号)“覆盖”的,而且像素之间必须分离开,水平方向上可以通过沟道隔离像素。为了将像素与像素在垂直方向上隔离开,必须将四个栅极中的某一个栅极电压变为零。在该系统应用中,将A1保持低电平,以起到像素隔离的作用。然而光生电荷在保持高电平的A2,A3,A4栅极下积聚起来,形成信号电荷包。

评论