用低成本FPGA解决高速存储器接口挑战

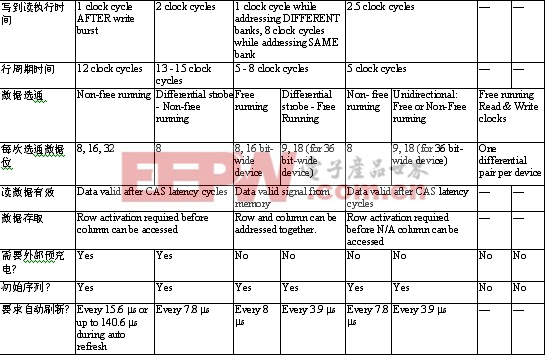

图1显示了典型的网络架构。在10Gbps,一个读写比为1000:1的地址查找可很容易地在DDR SRAM中得到处理。连接列表管理、流量修整、统计收集任务通常具有平衡的1:1读写比,需要较高性能的QDR SRAM。另一方面,较大的缓冲存储器一般在DDR SDRAM中实现。作为DRAM的替代,SDRAM同步存储器访问的处理器时钟用于快速数据传输。达到快速是因为SDRAM允许存储器的一个块被存取,而另一个块准备被存取。与DRAM不同,SDRAM采用流动电流而不是存储电荷,除去了连续刷新的需要。

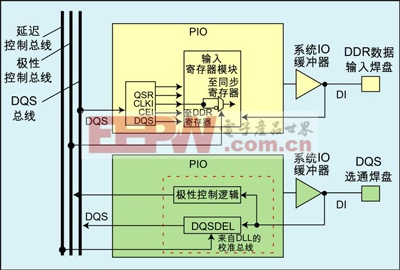

图2:LatticeEC FPGA中的专用DQS电路。

两个新的竞争者进入了高精度存储器舞台。快速周期随机存取存储器(FCRAM)改进了性能,它采用了流水线操作和隐蔽的预充电技术以减少随机存取周期时间,高度分段的存储器核减少了功耗。存储器核分段为较小的阵列,这样数据可以被很快地存取并改进执行时间。这些特征使得FCRAM被理想地用作缓冲存储器,用于诸如交换、路由和网络服务器等的高速网络应用中。时延减少的DRAM(RLDRAM)提供SRAM类型的接口以及非多路复用的寻址。RLDRAM II技术提供最小时延并可减少行周期时间,这些特征很适用于要求关键响应时间和快速随机存取的应用,例如下一代10Gbps以及更加高速的网络应用。

存储器控制器的挑战

目前存储器接口经常要求时钟速度超过200MHz以满足线卡和交换卡的吞吐量要求,这是FPGA架构的主要挑战。PLL是基本的允许控制时钟数据关系的部件。

下一代存储器控制器工作在HSTL或SSTL电压。低电压电平的摆动是需要的,以便??持存储器和存储器控制器的输入输出的高速数据操作。对于高速SRAM存储器来说,HSTL是实际的I/O标准,而对于高速DDR SRAM存储器,SSTL是实际的I/O标准。

高速差分I/O缓冲器和专用电路的组合能够在高带宽下进行无缝读写操作,传统上这属于高级FPGA的领域。LatticeEC FPGA改变了那个惯例,通过低成本FPGA架构实现了高带宽存储器控制器。

表1:为用于高速网络应用的存储器综合比较。

DDR存储器控制器的支持

评论