基于FPGA技术实现与PC串行通信

控制模块本文引用地址:http://www.amcfsurvey.com/article/192024.htm

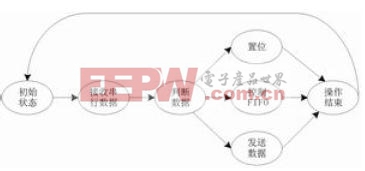

主要实现的功能是:判断从PC接收的数据,根据预先设计的逻辑进行相应的状态转换。例如:给端口预置一个状态;送开始发送的标志位,送准备发送的数据;给DDS送配置信号,控制FIFO的读写。程序中状态机设计如图3所示。

图3 状态机变换

设计中需要注意的问题

波特率的选择对于串口通信是很重要的,波特率不应太大,这样数据才会更稳定。整个发送接收过程中起始位的判别和发送是数据传输的前提。为了避免误码的产生,在FPGA设计中的串行输入和输出端口都应该加上一个数据锁存器。

仿真结果

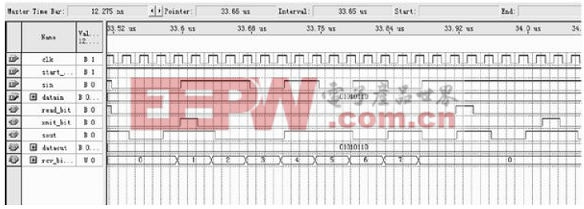

基本的发送接收如图4所示,clk是时钟信号(57600 bit/s);start_xmit是开始发送标志位;sin是串行输入;datain是并行输出;read_bit是接收结束标志位;xmit_bit是发送结束标志位;sout是串行输出;dataout是并行输出;rcv_bit 是接收位数寄存器。发送接收模块主要完成把从sin端口接收的串行数据变为并行数据送给dataout;把并行数据datain变成串行数据通过sout端口串行发送。

图4 发送接收过程

接收:判断接收的串行数据sin是否是连续的两个0,如果是则进入接收过程;每两个时钟周期接收1个比特的数据,依次接收到01101010,如果接收到停 止位表明这个接收过程结束read_bit=1。根据串行通信协议,数据是按照先低位,后高位的顺序发送的,所以实际接收的是01010110。发送:待发送的并行数据为01010110,当start_xmit=1发送有效,进入发送过程;首先发送两个起始位0,保证长度为两个时钟周期,然后依次发送01101010,每两个时钟周期发送1比特,最后发送停止位,发送过程结束xmit_bit为1。

发送控制字

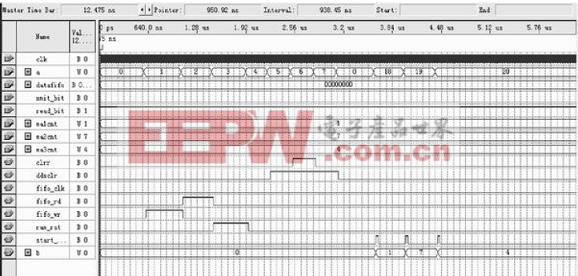

图5中clk是时钟信号;a是PC发来的16进制的控制字,也就是图4中的并行输出dataout; ma1cnt、ma2cnt、ma3cnt是三个寄存器;clrr是系统清零信号;ddsclr是DDS配置信号;fifo_clk,fifo_rd,fifo_wr,ram_rst是FIFO的时钟、读、写、清零信号;start_xmit是发送开始标志位;b是准备发送的数据。当接收a为1时,fifo_wr置1;当a为18时,把ma1cnt的值送到b。其他的操作类似,主要是端口的置位,FIFO读写状态的控制。

图5 发送控制字过程

从FIFO中读写数据

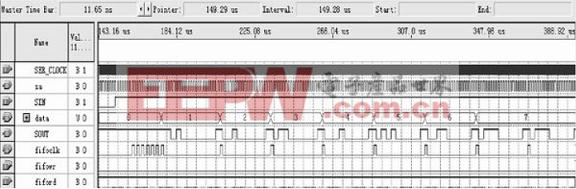

图6中SER_CLOCK是系统时钟3.6864MHz,sa是分频后的频率57600bit/s;SIN是串行输入;data是准备输出的数据;SOUT是串行输出;fifoclk、fifowr、fiford是FIFO的读时钟、写、读使能。读过程:读使能有效,先产生6个读时钟,但是不往SOUT发送数据,因为FIFO的前6个周期不是有效数据。然后产生一个读时钟,将FIFO的数据送到data,按照通信协议通过SOUT发送出去,发送结束再产生一个读时钟,读取FIFO的数据,进行下一次串行输出。

图6 从FIFO读数据的过程

结语

随着可编程器件的不断发展和广泛应用,FPGA与外围设备的通信也越来越多。本文介绍的串行通信的实现具有可复制性,只需改变系统时钟频率和控制模块就可以在其他场合下使用。

评论