高速FPGA系统的信号完整性测试和分析

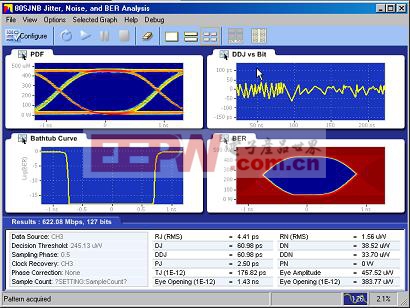

80SJNB软件除了能够得到每一个抖动和噪声分量的精确结果,针对设计和测试人员还提供了各种图形显示进行更细致的信号完整性分析。例如,抖动和噪声成分概率分布, 频谱分布, 数据相关抖动和噪声与位的关系, 数据码型波形, 抖动和噪声浴缸曲线, BER概率图, BER轮廓图, 概率分布眼图。图5是得到的分析结果。本文引用地址:http://www.amcfsurvey.com/article/192023.htm

图5 80SJNB软件得到的分析结果

5. 高速并行总线的眼图测试

对于FPGA芯片提供的高速并行总线,由于其数据传送方式并没有采用内嵌时钟的方法,时钟可以作为触发信号,观测多路并行总线的眼图。由于并行总线的通道数比较多,在示波器中手工测试多通道的眼图比较繁琐,有些传统逻辑分析仪虽然能够直接进行并行总线的眼图测试,但无论是测试精度和速度都无法和示波器进行的标准眼图测试相提并论。

除了能够通过FPGAView对简化FPGA的在线调试,TLA逻辑分析仪能够配合TDS示波器对FPGA外部信号自动进行多通道的眼图测试和分析,该功能称为iVerify眼图测试,最多可以自动的测试408个通道的眼图。

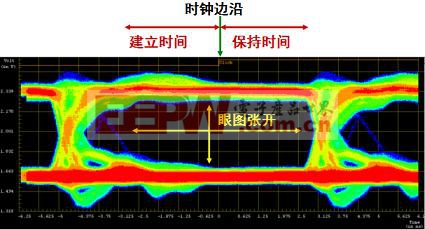

泰克为逻辑分析仪和示波器集成提供了一个信号完整性测试工具包,称为iLink工具包,分为iConnect,iView,以及iVerify眼图测试三个工具。iVerify是建立在iConnect技术和iView技术的基础上,它能够自动对多路并行总线进行眼图测试来彻底验证被测信号。结合iConnect技术,使用一套逻辑分析仪有源探头进行信号逻辑和模拟的同时观测,逻辑分析仪可以将被测通道分成多组,每一组3个数据通道送入到示波器中进行眼图测试,示波器的第4个通道作为外部时钟;采用iView技术,逻辑分析仪可以自动的将每一次送入示波器的3个数据信号的眼图测试数据会传到逻辑分析仪中,这样逻辑分析仪就可以再选择另外一组3个通道进行测试,对于复杂的高速总线,可以一次测试408个数据通道。最后,iVerify技术通过逻辑分析仪将最多408个数据信号的眼图测试数据叠加显示出来,彻底验证总线中出现的信号完整性问题。图6是在TLA逻辑分析仪上自动累计的多个通道眼图数据的色温显示。

图6 TLA逻辑分析仪上显示多通道眼图测试结果

6. 小结

对于FPGA中的高速串行和并行IO信号,需要根据被测信号特点和速度来选择合适的测试和分析工具。当测试信号完整性,希望得到最精确的上升时间,下降时间,信号过冲和震铃等参数,带宽是首要选择。某种意义上带宽越高,测试精度越高。对于实时示波器而言,高速采集内存是眼图和抖动等信号完整性测试的关键。对于采样示波器,通过CSA/TDS8200配合80SJNB抖动和噪声分析软件,不仅可以精确的测量高速串行信号的抖动和噪声,并且能够根据测量结果进行精确的抖动、噪声中每一个分量的分离,和系统的BER相关,最终为信号完整性验证人员提供有价值的信息。当测试高速时钟或数据抖动时,泰克两种示波器都配备业内推荐的抖动测试和分析软件,帮助设计人员得到抖动结果,分析抖动产生的原因,最终得到高可靠性的系统。

评论