高速FPGA系统的信号完整性测试和分析

1. 引言

本文引用地址:http://www.amcfsurvey.com/article/192023.htm 随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物理链路的速度从200Mbps到高达10Gbps,高速IO的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员面临的巨大挑战。这些挑战使设计人员非常容易会把绝大部分设计周期时间放在调试和检验设计上。

为了加速对于FPGA中高速并行和串行总线的调试和验证,它需要使用新的高速信号完整性测试工具和分析方法。本文根据当前FPGA的高速总线测试和分析,提供了最新的方法和工具。

图1是一个典型FPGA的提供的各种高速接口。对于这些速度从200M到高达10G的高速总线,信号完整性的测试和分析是保证设计成功的基础和关键。

图1 典型FPGA的提供的各种高速接口

2. 高速串行总线眼图测试

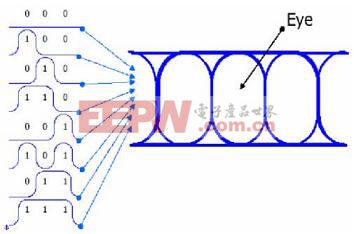

对于采用内嵌SERDES电路的FPGA芯片,其高速串行信号进行测试和验证,最基本的工具是通过示波器进行对其眼图测试。因为眼图能够非常直观的反映一条被测信号路径上的整体信号质量问题,包括信号的抖动量大小(眼宽)以及幅度的大小(眼高)等重要信息。图2是一个高速数据信号的眼图形成的过程。

图2 眼图的形成过程

从眼图的形成过程可以看出,一个NRZ编码的高速数据无论传输何种码流,都可以看作一个重复信号,经过一定时间和样本数的累计,它反映整个传输链路上的总体信号质量。

3. 选择合适的眼图测试工具

3.1 示波器带宽的要求

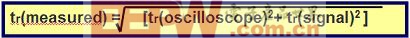

示波器是进行高速串行信号眼图测试的首选工具。无论是用高速实时示波器还是采样示波器(Sampling Scope)得到眼图,带宽是对示波器的基本要求。以一个NRZ编码的高速串行总线为例,它理想的波形是一个方波信号,方波信号是由它的基波(正弦波)和奇次谐波(3次,5次,7次…)组成。根据信号的传输速率和上升时间,选择尽量高带宽和最快上升时间的示波器,这样测试结果保留更多的谐波分量,构建高精度的眼图测试结果。

示波器带宽反映了对被测信号幅度上的衰减,而示波器上升时间决定了对被测信号上升时间测试的误差。经典的示波器带宽和上升时间的关系为:带宽×上升时间=0.35-0.45,0.35-0.45为常系数。每一个高性能示波器除了提供带宽的指标外,还会给出上升时间,表征其对阶跃信号的测试能力和精度。示波器测试结果的经验公式为:

评论