VGA时序发生器设计

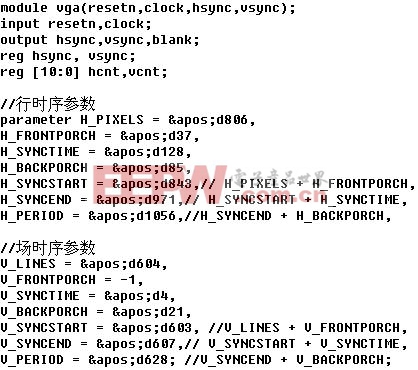

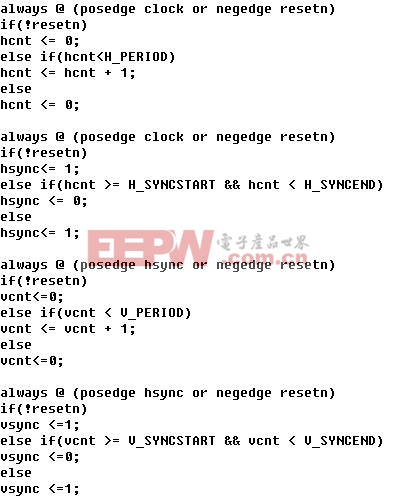

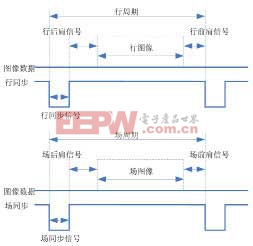

VGA标准时序参考图如图7所示,并用VERILOGHDL设计For VESA 800*600 @ 60Hz:VGA时序的源代码:

图7 VGA标准时序参考图

系统分析

经过反复测试,系统能够将采集端数据实时传送到显示器上,具体性能指标如下:

视频输出:VGA视频输出

视频显示DA转换精度: 10bit

图像输出标准: SVGA(75Hz, 800×600)

显示分辨率: 10bit

结语

该VGA视频显示系统不但可以稳定地采集图像数据,而且可以实时将数据传输到CRT显示器,便于以后人工综合分析、处理。它特别适用于大型商场等显示端,可以说是一个理想的解决方案。

评论