基于FPGA的串行接收模块的设计

1 前言

随着FPGA的飞速发展与其在现代电子设计中的广泛应用,越来越多的实验和设计中会运用FPGA与RS232通信。与此同时, FPGA具有功能强大、开发过程投资小、周期短、可反复编程等特点。笔者在FPGA芯片上集成了串行接收功能模块,从而简化了电路、缩小了电路板的体积、提高了可靠性。本文主要介绍围绕FPGA所设计的符合 RS232标准的串行接收模块。

2 异步串行通信原理

串行通信分为两种类型:同步通信方式和异步通信方式。本设计采用的是异步通信方式,其的特点是:通信的发送方和接收方各自有独立的时钟,传输的速率由双方约定。国际上规定的一个串行通信波特率标准系列是:110、300、600、1200、1800、2400、4800、9600、 19200,单位是 bps。本文采用的是 19200bps。

异步传输是一个字符接一个字符传输。一个字符的信息由起始位、数据位、奇偶校验位和停止位组成。每一个字符的传送靠起始位来同步,字符的前面是一位起始位,用下降沿通知接收方传输开始,紧跟着起始位之后的是数据位,传输时低位在前、高位在后,字符本身由5~8位数据位组成。数据位后面是奇偶校验位,昀后是停止位,停止位是高电平,标志一个字符的结束,并为下一个字符的开始传送做准备。停止位后面是不定长度的空闲位。停止位和空闲位都规定高电平,这样可以保证起始位开始处有一个下降沿,如图1所示。 3 硬件接口电路原理设计

在串行通信中,普遍采用的是 RS232-C接口的标准。 RS232-C接口信号引脚的连接方式规定了25芯的D型连接器DB-25,本设计采用的是一个 9芯的D型连接器DB-9,并且用昀为简单常用的三线制接法,即地、接受数据和发送数据三脚相连。

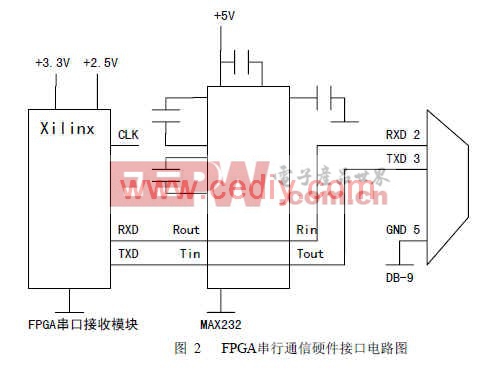

本设计的硬件接口电路图如图2所示,由三部分组成: FPGA串口接收模块、 MAX232和DB-9。FPGA采用的是Xilinx公司的SPARTAN系列的 XC2S50芯片,其封装为TQ144。 MAXIM公司的MAX232CPE是为满足EIA/TEA-232E的标准而设计的,具有功耗低、波特率高、价格低等优点。工作电源为 +5V,外界电容仅为 luF,为双组 RS-232收发器。MAX232有两个发送器,本设计只用其中一个发送器,另外一个发送器的输入端接地、输出端悬空。

异步数据接收过程可作为一个整体来实现,数据由 DB-9的RxD端输入,经过 MAX232进行电平转换由FPGA串口接收模块的 RxD端进入,然后在串口接收模块内部对接收来得数据进行判断,并昀终实现对FPGA输出信号的控制。

评论