基于FPGA和DSP的卫星导航接收机测试平台

引言

卫星导航接收机是卫星导航系统的用户终端,用以给用户提供精确的经度、纬度、高度和速度等信息。现在,卫星导航接收机已经应用于航空,交通管理,石油等各个领域,针对卫星导航接收机的研究也越发深入。

本文介绍了一种以 FPGA和 DSP为主处理器的卫星导航接收机硬件平台。在该平台上不仅可以验证针对现在所有卫星导航系统(GPS,Glonass,伽利略,北斗)的基带信号处理算法和导航解算算法,同时也可以实现完整的单频、双频或者兼容接收机。

1 硬件设计

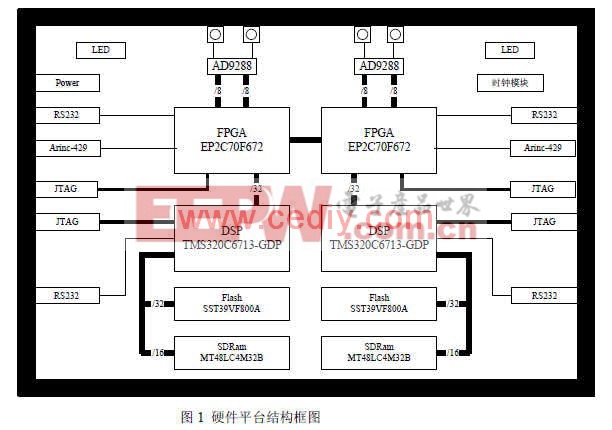

1.1 硬件平台组成硬件平台结构框图如图 1所示。

该平台以两片 FPGA芯片和两片 DSP芯片为主处理器。经过 AD采样后的信号直接进入FPGA,此后所有对信号的处理均由软件来实现。如此可以充分利用 FPGA和 DSP的重复烧写及在线调试能力,

尽量减少对硬件的依赖程度,从而增加平台的灵活性。另外,每片 DSP都外接了 Flash和 SDRAM。由于 Flash掉电数据不会丢失,可以在 Flash内保存程序及数据,功能有如 PC机上的硬盘,而外接的 SDRAM是 DSP的扩展Ram,当 DSP运行大型程序(如导航解算程序)以致 DSP的内部 Ram不够用时,可以将程序放到外接的 SDRAM内运行。

平台上还有多个串口,可以接显控等设备。两个 Arinc-429接口可以接惯导等航空设备。JTAG是在线调试接口。时钟模块提供系统的工作时钟。

只要连接上针对不同卫星导航系统的射频模块和天线,该平台就可以成为一个完整的接收机。

1.2 芯片介绍

FPGA采用 Altera公司 CycloneII系列中的 EP2C70F672。Altera公司的 CycloneII系列 FPGA是业界成本及功耗最低的 FPGA之一,采用 90nm工艺制造。 EP2C70F672是 CycloneII系列中的最高型号,拥有 7万个逻辑单元, 1Mbits内部 RAM,300个 9×9乘法器,4个 PLL环和 422个 I/O接口,最高数据率可以达到 330Mbps。

DSP采用德州仪器公司(TI)的C6000系列中的TMS320C6713。它是TI开发的基于甚长指令(VILW)结构浮点运算数字信号处理芯片,每周期可以执行 8条32位指令,工作频率最高可以达到300MHz。拥有 256K字节内部RAM,16个通道的增强 DMA控制器,32bits外部存储器接口,两个多通道缓冲口。

模数转换芯片选用模拟器件公司(ADI)的 AD9288Bst-100。该芯片的采样率最高可以达到100Msps,正交双通道 8bits输出。由于其低功耗特性,被广泛应用于手持设备等对功耗要求较高的场合。

Flash采用SST公司的 SST39VF800,容量为 512K*16。SDRAM采用 Micron公司的 MT48LC4M32B,存储空间为4M*32。

2软件测试

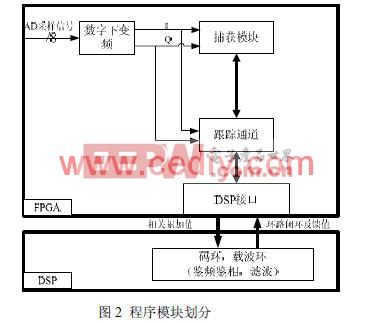

在该硬件平台上用 Verilog语言和 C语言编写了简单的 GPS卫星捕获跟踪程序,以验证其功能。程序模块划分如图 2所示。在 FPGA内实现了数字下变频,捕获和跟踪通道,在 DSP内实现跟踪环

路的鉴频鉴相算法以及环路滤波器。经过 A/D采样的 8bit信号通过下变频模块后输出 I/Q两路正交基带信号。I/Q基带信号分别进入捕获模块和跟踪通道模块。在成功捕获到信号后转入跟踪。跟踪通道每次输出的相关累加值经过 DSP接口模块传给 DSP。DSP利用接收到的相关峰值进行鉴相鉴频和滤波,并将滤波结果反馈给 FPGA形成闭环。

评论