FPGA配合预失真技术的解调误码测试仪

3.2.2QPSK解调模块

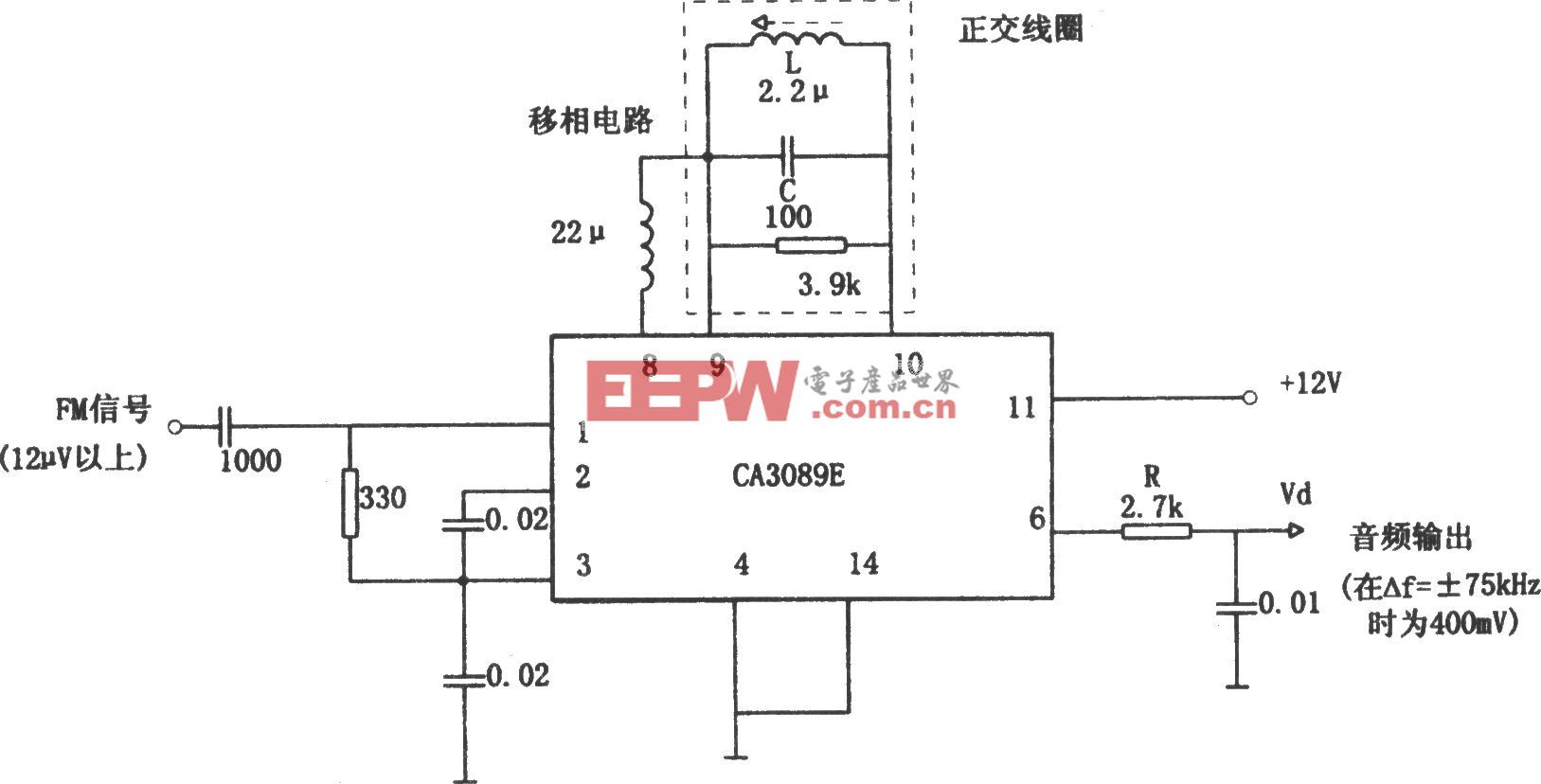

接收信号经接收板的 A/D转换后将两路 10位二进制信号同时送入 FPGA处理,流程如图 1中接收系统所示。

判决模块将滤波器整形后的 10位 I、Q路信号通过门限判决,映射为 1或 0两种码,判决的门限值我们根据实践设定。随后经过并/串处理后便得到解调数据。

3.2.3 预失真器

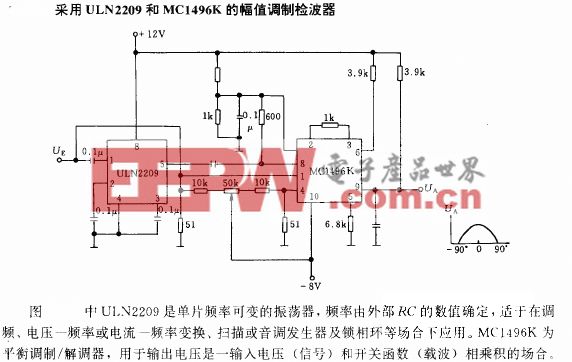

本方案采用查表法来实现预失真器,即使用两个独立的一维表――幅度表和相位表来近似逼近放大器非线性的逆函数,这两个表由两块 RAM组成。预失真器根据输入信号的幅度计算查询表地址,并利用地址来查找相应的增益和相位,对输入信号增益进行补偿,然后再做相位旋转得到预失真器的输出。

图 1中的预失真误差计算模块由反馈信号通过自适应算法来更新查找表。该算法基于乘法,相较于基于加法的预失真器,乘法对于反馈信号的相位不敏感,在反馈路径中不需要相位调整电路。若预失真器的输入 x(n)是幅度 ρ(n),相位 φ(n)的复信号,经过量化限幅后其地址输入为 Q[ρ(n)];若预失真器的输出 z(n)是幅度 r(n),相位 θ(n)的复信号,可得: z(n)=r(n)exp[ jθ(n)] = Kn ρ(n) exp[ j(φ(n) +ψn)],式中 Kn和 ψn分别是查询表的地址映射值。查询表内容的昀终迭代关系式: Kn+1 (Q[ρ(n)]) = Kn(Q[ρ(n)])-α(A[r(n)]/ρ(n)-1) 和 ψn (Q[ρ(n)]) =ψn(Q[ρ(n)])-β(ω(n)-φ(n)),式中 α和 β是迭代步长,调整它们可以调节收敛速度。预失真器通过对以上两式的迭代,不停的更新查询表内所存储的数值,以达到对 HPA反函数曲线的逼近。

为了提高收敛速度,在本方案中采用了基于插值法的查询表内容更新策略:每一次递归并不仅仅改变当前地址的查询表内容,而是通过相应的调整策略更新相关联的多个地址的查询表内容。在实现时,使用一个与查询表地址数目一致的地址更新指示器,若地址 N位置的数据已经过迭代,则指示器对此进行纪录;同时从 N位置向上和向下进行搜索,查找距离 N地址位置距离昀近的,且同样已经过迭代的两个地址位置 N-L1和 N+L2,二者之间其它地址的存储数据可以通过线性内插得到: D´(N-n)=(1-n/L1)D(N)+ n/L1D(N-L1), (1≤n≤L1)和 D´(N+n)=(1-n/L2)D(N)+ n/L2D(N+L2) , (1≤n≤L2)。

3.2.4 测误码模块

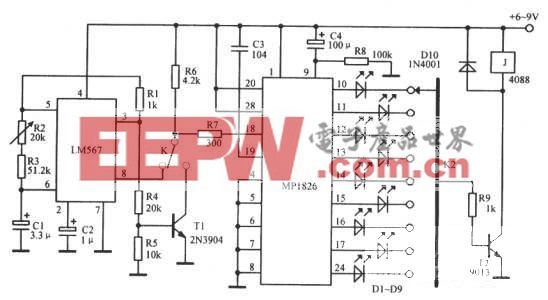

我们需比较发送数据与接收数据从而得到误码数,以作为昀终的硬件设计评估指标。在接收板的 FPGA中,添加测误码模块就非常的必要。图 2表示出了其具体的实现和组成。

此处的本地 m序列产生器与发射端的设置相同,就相当于产生发送数据,由于其与解调模块共用同一时钟,我们便可将解调出的数据与该序列同时送入逐位比较检测模块进行比较。

为保证解调数据与序列产生器发出的码帧对齐,还需设置帧头判断模块,当判断出解调数据的帧头到来时便启动本地 m序列产生器开始比较。逐位比较检测模块由异或门构成 ,在时钟上升沿到来时 ,若比较控制信号为 “1”,则将接收序列和本地序列进行异或比较 ,有误码 ,则输出“1”。比较控制信号由帧头判断模块产生,当判断到帧头时,其跳变为 “1”,控制误码测试启动,统计若干帧再次检测到帧同步头时,其跳回“0”,结束检测。

误码统计模块对误码进行计数,当比较控制信号为“0”时即结束计数并输出误码数。

4 测试结果

由于解调涉及到载波同步与时钟同步问题,我们将讨论用一种昀简易的方法实现。时钟同步的解决:将接收板系统所需的时钟接到发射板的晶振上,以保证同频。载波同步的解决:在晶振相同的前提下我们可以保证 VCO载波同频,但相位会有偏差,因此我们需要在 FPGA中添加一块锁相环以保证本地载波的相位跟踪上发射载波。

同步问题解决后,我们首先采用 Chipscope观看进入 FPGA的 I、Q两路的幅频(A-F)特性图,从而根据其幅度的分布为判决门限规定具体的值。同时,观看星座图以了解解调效果是否满足需求,图 3即为本系统在码速率 40Mbps时经解调所得的星座图。

在实验室的情况下,预计误码率的数量级在 10-12左右,为提高测量的可靠性,本次测试选取 3×1014个帧作为一次检测周期。多次测量结果并没有出现误码情况,硬件设计满足工程要求。5 结束语

本文旨在讨论一些实际的硬件测试经验,并对整套测试工作进行详细的归纳与总结,提出了可供工程师参考的解决方法。QPSK技术目前在卫星数字通信中广泛应用,本文则通过讨论 QPSK成套的调制解调系统,着重阐述了该测试系统的硬件及 FPGA的设计与实现。该测试系统可以有效地帮助工程师进行设备互通测试和工程验收。

评论