用FPGA技术实现模拟雷达信号

前言

本文引用地址:http://www.amcfsurvey.com/article/191955.htmFPGA(现场可编程门阵列)是由掩膜可编程门阵列和PLD(可编程逻辑器件)演变而来的,并将二者的特性结合在一起,使FPGA既有掩膜可编程门阵列的高逻辑密度和通用性,又有PLD的可编程特性。FPAG技术的发展使得单个芯片上集成的逻辑门数越来越多,能实现的功能越来越复杂。它以编程方便、集成度高、速度快等特点受到电子设计人员的青睐。人们可以通过硬件编程的方法设计和开发ASIC(专用集成电路)芯片,极大地提高芯片的研制效率、降低开发费用。

通过应用FPGA技术,较好地为“某型雷达告警设备”的配套检测仪器实现了模拟雷达信号发生器ASIC芯片的设计,该芯片能够提供“某型雷达告警设备”测试过程中所需的多种典型的重频脉冲及制导信号等,其中包括SA-6重频信号、SA-2重频脉冲及制导信号、SA-3重频脉冲及制导信号、雷达脉冲视频等。所设计的ASIC芯片的性能较为理想。

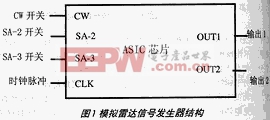

模拟雷达信号发生器的结构如图1所示。可以看到,模拟雷达信号发生器由连续波雷达模拟信号CW开关、制导信号SA-2开关、制导信号SA-3开关、时钟脉冲产生器、输出1、输出2和产生模拟雷达信号的控制芯片组成。上述开关都是高电平有效,开关的消抖动电路放在控制芯片部分考虑。时钟脉冲产生器由外部的晶体振荡器产生一个频率稳定的1MHz时钟脉冲,用来满足信号脉冲宽度的要求。“CW开关”有效时,“输出2”输出连续波雷达达模拟信号;“SA-2开关” 有效时,“输出2”输出SA-2的重频脉冲,“频脉冲,“输出1”输出SA-2的指令信号组;“SA-3开关”有效时,“输出2”输出SA-3的重频脉冲,“输出1”输出SA-3的指令信号。

ASIC芯片的设计

1芯片主要性能指标

(1)产生连续波雷达模拟信号:重频3012Hz,脉宽1μs±0.1μs;

(2)产生制导信号SA-2重频脉冲:重频2463Hz,脉宽0.5μs±0.1μs;SA-2指令信号组:重频2463Hz,每秒132个单指令,44个指令组,指令脉宽1μs±0.1μs;

(3)产生制导信号SA-3重频脉冲:重频3497Hz,脉宽0.5μs±0.1μs;SA-3指令信号同SA-3重频脉冲等。

评论