在FPGA上对OC8051IP核的修改与测试

引 言

20世纪80年代初,Intel公司推出了MCS-51单片机,随后Intel以专利转让的形式把8051内核发布给许多半导体厂家,从而出现了许多与MCS-51系统兼容的产品。这些产品与MCS-51的系统结构相同,采用CMOS工艺,因而常用80C51系列来指代所有具有8051指令系统的单片机。在80C51系列中,OC8051以架构清晰、取指带宽大、时钟效率高等诸多优点受到业内人士的青睐。本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

1 OC8051结构分析

OpenCores网站提供的OC8051 IP核与8051的系统结构相同,如图1所示。该IP核兼容所有8051指令系统,内部资源包括:8位CPU,寻址能力达2×64K;4 KB的ROM和128字节的RAM;4个8位I/O口;16位内部定时/计数器;5个中断源和2个中断优先级。采用Verilog语言对其各个模块进行描述。系统主要模块及其功能说明如表1所列。不同模块对应的源文件均是以模块名称命名的,例如累加器A对应的源文件为oc8051_acc.v。

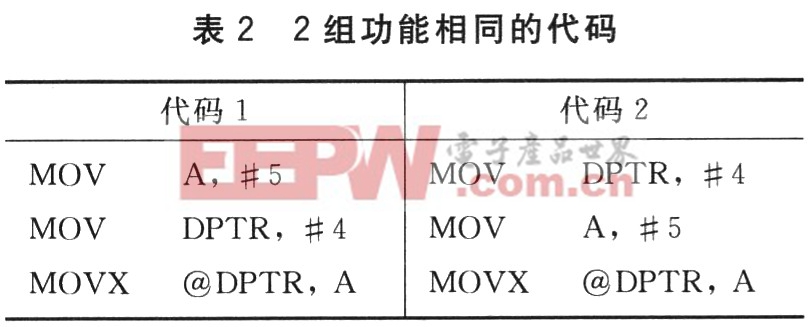

虽然上述OC8051 IP核宣称兼容所有8051指令系统,但是实际执行时并非如此。例如在执行表2所列的2组功能相同的代码时,所得到的执行结果并不相同。代码1的执行结果是将5写入地址为0的外部RAM,代码2的执行结果是将5写入地址为4的外部RAM。造成这种现象的原因是,oc8051_ext_addr_sel模块配置写外部RAM地址时延误了一个时钟周期。若要OC8051 IP核与标准8051系统一致,须对源文件中类似的逻辑错误进行修改。

|

|

2 OC805 1仿真调试及修改

对于硬件设计而言,仿真的作用是验证设计结果的逻辑功能是否符合初始规定,如果在这一层次上设计出了问题,那么以后各个层次的工作将完全不确定。由前文可知,OC8051 IP核存在着逻辑错误,所以有必要通过仿真的手段实现错误查找和定位,从而最终完成对逻辑错误的修改。

评论