基于FPGA快速A 律压缩编码的设计与实现

摘要:本文针对A律13折线法的算法特点,提出一种并行数据处理算法,实现了编码的流水线操作。运用VHDL语言将其在FPGA中实现,借助quartus II6.0平台进行验证,并对验证结果进行分析,评估了系统的性能,证实了该算法的优越性和高效性。

关键词:A律压缩编码,FPGA,VHDL

1引言

在信号处理过程中,我们通常将模拟信号转化为数字信号进行处理或传输。原始数据用取样的方法进行采集,通过A/D转换将模拟信号变成数字信号。但是这样的数字信号由于码位多,在传输过程中占用带宽多,传输率也低。为了提高传输效率,必须对原始数据进行量化处理。在实际运用中通常采用非均匀量化。采用输入信号幅度和量化输出数据之间定义了两种对应关系,一种是在北美日本使用的 律;另一种是在欧洲中国大陆使用的A律。A律压缩重要运用于数字电话通讯中的语音压缩编码,如何实现快速压缩已成为实际应用的关键。随着VLSI(超大规模集成电路)特别是FPGA技术的日益成熟,基于FPGA的各种压缩编码的实现显示出其独特的优势和广泛的应用前景[1-3]。本文针对13折线来的算法特点,提出一种并行数据处理且适合于实现编码流水线作业的改进算法,运用VHDL语言将其在FPGA中实现,借助Quartus II 6.0平台对其进行验证、仿真,并对仿真结果进行分析,评估了系统的性能,证实了该算法的优越性和高效性。

2 原理

所谓A压缩律也就是压缩律具有如下特性的压缩律[4]:

:

:

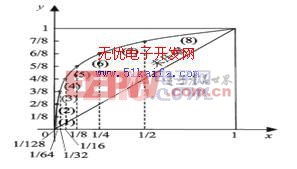

式中x ―归一化的压缩器输入电压; y―归一化的压缩器输出电压; ―压扩参数,表示压缩程度。实际中, 压缩律通常采用13折线(图1)来近似。

图1 13折线示意图

评论