基于流水线技术的并行高效FIR滤波器设计

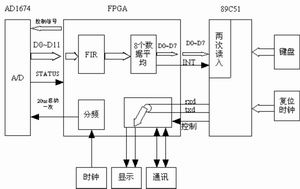

摘要:基于流水线技术,利用FPGA进行并行可重复配置高精度的FIR滤波器设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用这种FIR滤波器的设计方法可以充分发挥FPGA的优势。

本文引用地址:http://www.amcfsurvey.com/article/191651.htm数字滤波器可以滤除多余的噪声,扩展信号频带,完成信号预调,改变信号的特定频谱分量,从而得到预期的结果。数字滤波器在DVB、无线通信等数字信号处理中有着广泛的应用。在数字信号处理中,传统滤波器通过高速乘法累加器实现,这种方法在下一个采样周期到来期间,只能进行有限操作,从而限制了带宽。现实中的信号都是以一定的序列进入处理器的,因此处理器在一个时钟周期内只能处理有限的位数,不能完全并行处理。基于并行流水线结构的FIR滤波器可以使笔者设计的64阶或者128阶滤波器与16阶滤波器的速度一样快,其显著特别是在算法的每一个阶段存取数据。FPGA结构使得以采样速率处理数字信号成为常数乘法器的理想载体,提高了整个系统的性能。由于设计要求的差异,如字长、各级输出的保留精度等不同,在整个设计过程中,各个环节也有所不同,这就需要根据不同的要求对数据进行不同的处理,如截断、扩展等,从而设计出既满足设计需要,又节省FPGA资源的电路。. .

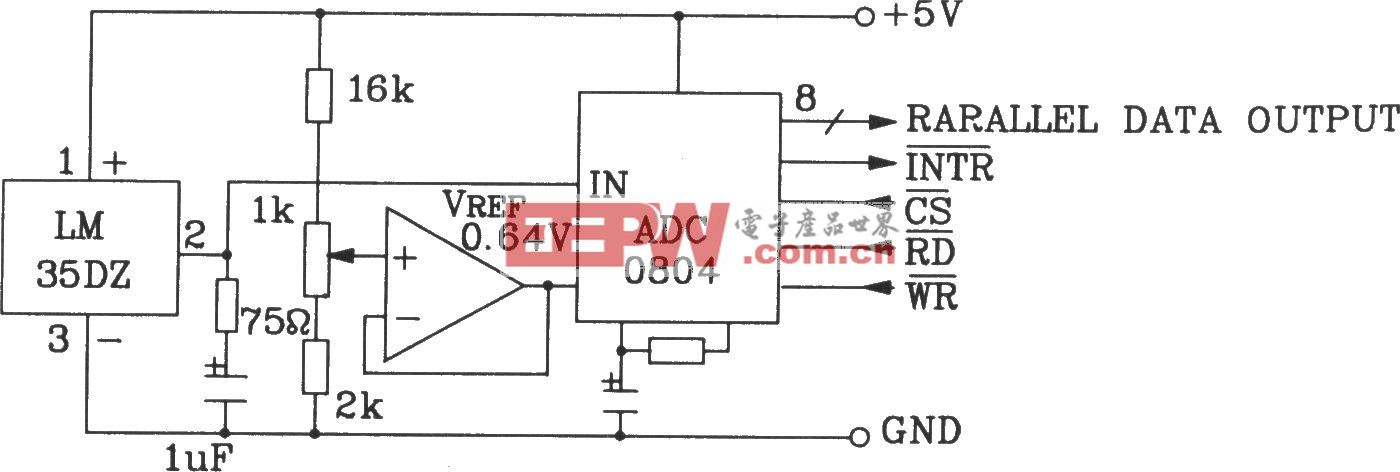

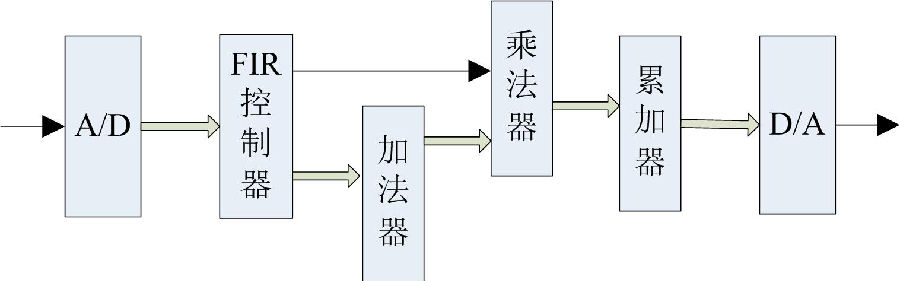

图1 并行滤波器结构

1 FIR并行滤波器结构

数字滤波器主要通过乘法器、加法器和移位寄存器实现。串行处理方式在阶数较大时,处理速度较慢。而现代数字信号处理要求能够快速、实时处理数据,并行处理数据能够提高信号处理能力,其结构如图1所示。

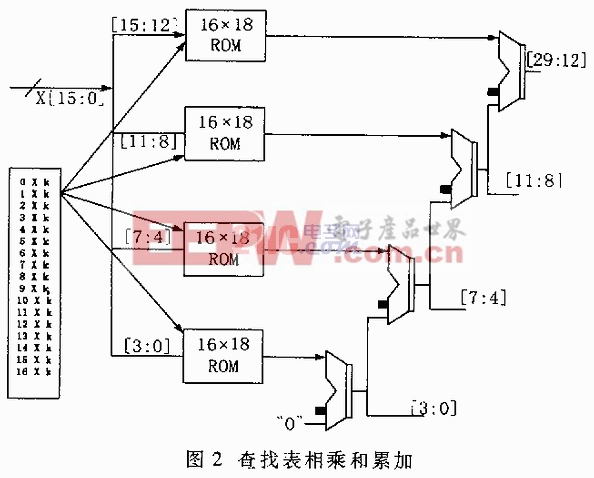

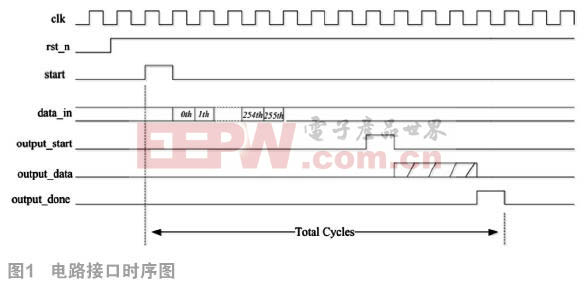

图2 查找表相乘和累加

从上面的算法可以看出,处理数据的采样时钟对每一个抽头来说都是并行的,并且加法器和移位寄存器采用级联方式,完成了累加器的功能,综合了加法器和移位寄存器的优点,而且这种算法的各级结构相同,方便扩展,实现了任意阶数的滤波器。算法中,真正点用系统资源的是乘法器。如果将系数量化成二进制,就能采用移位寄存器和加法器实现乘法功能。对于一个特定的滤波器,由于它有固定的系数,乘法功能就是一个长数乘法器。下面将讨论乘法器的设计问题。

评论