MAX1032结合CPLD的应用

本文引用地址:http://www.amcfsurvey.com/article/191480.htm

本文引用地址:http://www.amcfsurvey.com/article/191480.htm

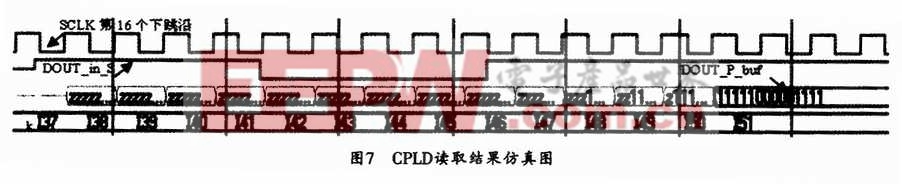

图7所示是Moddsim仿真的CPLD读取MAX1032的采样结果并将其存入寄存器DOUT_P_buf的仿真图。由图可见,在启动采样后的第16个SCLK的下跳沿,MAX1032输出14位串行采样结果,CPLD将其存入内部寄存器中以待系统读取。一般在下一次采样之前,需要将CPLD复位来清除上一次采样的数据。由于外部时钟模式下的SSTRB始终为低,故本例没有对该信号进行处理。

5 结束语

本文介绍了利用CPLD控制MAX1032进行采样的实现方法,包括CPLD的内部逻辑设计和对采样信号的处理等。实验证明,该方法能够适用

需要使用CPLD控制外围电路的场合。

评论