基于FPGA 的低成本长距离高速传输系统的设计与实现

摘要:为解决目前高速信号处理中的数据传输速度瓶颈以及传输距离的问题,设计并实现了一种基于FPGA 的高速数据传输系统,本系统借助Altera Cyclone III FPGA 的LVDS I/O 通道产生LVDS 信号,稳定地完成了数据的高速、远距离传输。系统所需的8B/10B 编解码、数据时钟恢复(CDR)、串/并行转换电路、误码率计算模块均在FPGA 内利用VHDL 语言设计实现,大大降低了系统互联的复杂度和成本,提高了系统集成度和稳定性。

0、引言

在地质勘探、工业环境监测、大型科学实验等领域中需要将实时采集到的大量数据以较高的速率传输距离较远,复杂而庞大的数据传输任务给传输系统的设计带来极大的挑战。目前常见的远距离高速传输方案多采用较为复杂的光纤通道等方案,系统的成本、设计难度、体积和功耗都相对较大,限制了其应用场合。

LVDS(Low Voltage Differential Signaling)是一种小振幅差分信号技术,它允许单个信道传输速率达到每秒数百兆比特,其特有的低振幅及恒流源模式驱动只产生极低的噪声,消耗非常小的功率。LVDS 是目前常见的高速数据传输方案,但其多用于芯片间、背板间或设备间进行近距离的数据传输。

本文中提出的高速数据远距离传输系统方案以Altera 公司Cyclone III 系列低成本FPGA 芯片EP3C5E144C8 的为核心,以LVDS 信号为基础,通过增加信道编码、数据时钟恢复、预加重和均衡等技术,保证了数据传输的稳定性和同步性。保证采用UTP-5 双绞线为传输介质时传输速率不低于400Mbps,传输距离为50 米时上的,实现低成本的远距离高速数据传输。

1、方案总体设计

LVDS 信号一种低振幅高速差分信号,由于其电气特性决定了其传输距离有限。为了满足系统使用UTP-5 双绞线实现距离50m 的数据传输要求,需要通过增加预加重和均衡技术来恢复线路上传输的信号波形。由于传输距离较远且传输速率较高,无法直接采用传送位时钟信号和帧同步脉冲来保证系统同步。本系统采取接收端从接收数据中恢复时钟信号的方法简化系统设计方案。

系统整体设计框图如图1 所示,整个系统的核心模块包括了8B/10B 编码、CDR(时钟恢复)、并-串/串-并转换模块、LVDS 接口电路、电缆驱动器(Cable Driver)和电缆均衡器(Cable Equalizer)等。数据在发送端的FPGA 内经过8B/10B 编码,并-串转换经LVDS 模式的I/O 端口转化为LVDS 信号,然后经过线路驱动器芯片CLC001 预加重后,通过UTP-5 双绞线传出数据。接收端收到的信号经过均衡器芯片LMH0074SQ 均衡后进入FPGA,在接收端FPGA 内,数据先经过CDR 模块提取时钟信号,然后字对齐后经过串-并转换产生并行数据流,最后经过8B/10B 解码模块得到传输数据。

整个系统除电缆驱动器和电缆均衡器采用专用芯片外其它功能均在FPGA内部实现,从而极大的减小了系统的复杂度和PCB 板的面积。

图1 系统整体框图

2.FPGA 关键模块设计

FPGA 作为系统的核心芯片,根据系统整体方案的设计思路,FPGA 中含有的模块主要有信道编解码模块、数据时钟恢复模块、串/并转换模块。

2.1 信道编解码模块

在高速数据传输过程中,为了使数据时钟恢复模块中的数字锁相环能够得到足够充足的跳变沿信息,需要采用信道编解码技术消除或减少数字电信号中的直流和低频分量。8B/10B 编码是其中最常用的一种编码方式。

8B/10B 编码被广泛应用于多种高速串行通信协议中。它将8bits 的基带信号映射成10bits 的数据进行发送,防止在基带数据中过多的0 码流或1 码流。通过8B/10B 编码可以提高数据在链路上的传输的性能;使接收器可以正确地恢复时钟;提高码流中一个或者多个比特错误的检测能力;定义特定的码元使接收器能够正确地对齐码元。在本系统中分别在两块FPGA 中实现了8B/10B 编码模块和8B/10B 解码模块。

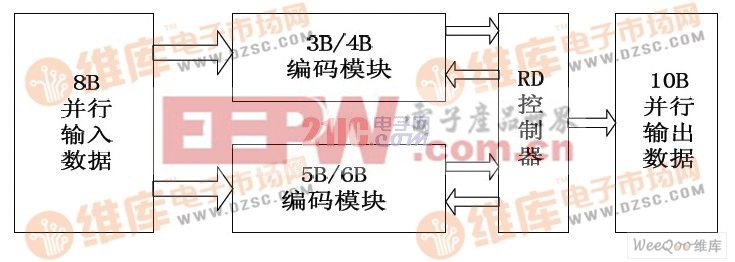

8B/10B 编码模块如图2 所示,该模块在逻辑上又分成3B/4B 编码模块、5B/6B 编码模块、RD 控制模块等3 部分。编码器首先将接收到的8B 数据分成3 bit 和5 bit 两部分,然后分别编码成4 bit 和6 bit,编码完成的4 bit 和6 bit 再按顺序组合成10B 码。整个系统首先将3 bit 编码成4 bit,RD 控制器读出4 bit 数据的RD 值,然后反馈控制5B/6B 编码模块选择合适的编码。最终RD 控制器判断10B 数据的RD 值,若满足要求则输出,否则将报错。

图2 8B/10B 编码模块逻辑框图

评论