基于FPGA的高速同步HDLC通信控制器设计

该方法编程简单,占用FPGA资源少,在一个模块内就能完成‘0’比特插入操作。

1.2 利用FIFO实现

遇‘0’缓冲实现法在传输大容量数据时,需要设置许多位缓冲,这样就耗费大量的FPGA内部资源,而且随着延时位数增加,门延时呈指数增长,累积到一定程度就会产生误差,所有当数据量大时,上述的方法就不再适用,可以利用FIFO实现。

当数据量大时,“积压”的数据相应也变大,可以利用FPGA内部资源FIFO节省逻辑资源,提高逻辑速度。选择异步FIFO,即读/写时钟不是同一个,这样可高速写入数据,再通过控制读时钟控制读的信息。

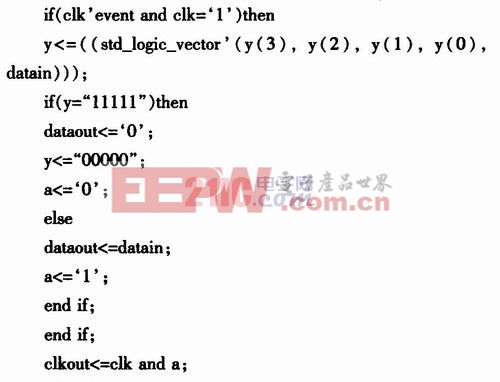

利用FPGA实现的VHDL代码为:本文引用地址:http://www.amcfsurvey.com/article/191467.htm

其基本思想是,一旦遇到5个连续的‘1’,就“抹掉”1个时钟,利用ISE 9.1i仿真的波形图如图3所示。

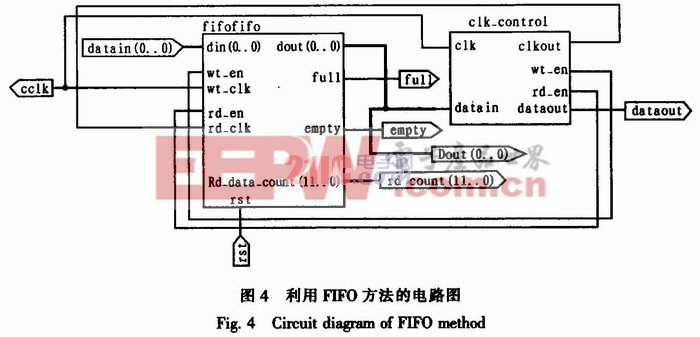

设计一个FIFO与上述VHDL代码产生的模块相连,电路图如图4所示。

利用ISE 9.1i仿真得到的波形图如图5所示。可看到对datain进行了‘0’比特插入操作,保证数据不丢失。而且该方法可根据所选器件的片内资源设置任意大容量的FIFO,并且当片内FIFO的存储量不够时,可先存入一部分数据,等FIFO读取一部分后,不满时再存入一部分数据。

‘O’比特删除操作是‘0’比特插入操作的反过程。在接收时为了还原原本的信息,就要删除发送时插入的‘O’。以逐位延时法为例,dataout最一开始输出延时了64个时钟周期的串行数据,i的初始值为64,当遇到‘lllll’时,i减1,输出延时了i个时钟周期的串行数据。而利用FIFO的方法就是遇到‘lllll’,抹去1个写时钟,将数据写入FIFO,再按规定的时钟把数据读取,当然写入的时钟可用较高的时钟周期。

2 CRC校验模块

帧校验字段用于对帧进行循环冗余校验,校验的范围从地址字段的第1个比特到信息字段的最后1个比特,但为了透明传输而插入的‘0’比特不在校验范围内。

CRC原理实际上就是在一个p位二进制数据序列之后附加一个r位二进制校验码,从而构成一个总长为n=p+r位的二进制序列,例如,P位二进制数据序列,r位二进制校验码,所得到的二进制序列就是,附加在数据序列之后的这个校验码与数据序列的内容之间存在着某种特定的关系。如果因干扰等原因使数据序列中的某一位或某些位发生错误,这种特定关系破坏,因此,通过检查这一关系,实现对数据正确性的检验。

要传输p=16位数据1001011010101011,选定的r=16的校验序列为10001000000100001,对应的FCS帧校验列是用100101101010101100000 00000000000(共p+r=32位)对2取模整除以10001000000100001后的余数1010100011000001(共有r=16位)。因此,发送方应发送的全部数据列为

10010110101010111010100011000001。接收方将收到的32位数据对2取模整除以r校验二进制位列10001000000100001,如余数非O,则认为有传输错误位。

评论