基于FPGA的高速同步HDLC通信控制器设计

摘要:高级数据链路控制HDLC协议是一种面向比特的链路层协议,具有同步传输数据、冗余度低等特点,是在通信领域中应用最广泛的链路层协议之一。提出实现HDLC通信协议的主要模块——CRC校验模块及‘0’比特插入模块的FPGA实现方法。CRC校验模块采用状态机设计方,而‘0’比特插入模块是利用FIFO实现,为HDLC通信控制器的设计提供新的思路。该方法已在Spartan3s400开发板上实现,并能正确传输。

关键词:HDLC协议;CRC校验;‘0’比特插入;FPGA

高级数据链路控制HDLC(High-level Data Link Control)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。实施HDLC的一般方法通常是采用ASIC器件和软件编程等。HDLC的ASIC芯片使用简易,功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。但由于HDLC标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。例如CCITT、ANSI、ISO/IEC等都有各种版本的HDLC标准,器件生产商都还有各自的标准,对HDLC的CRC序列生成多项式等有不同的规定。况且,专用于HDLC的ASIC芯片其片内数据存储器容量有限,通常只有不多字节的FIFO可用。对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC芯片再外接存储器或其他电

路,ASIC的简单易用性就被抵销掉了。

FPGA是现场可编程门阵列,属于超大规模集成电路,具有丰富的系统门、逻辑单元、块RAM和IO引脚等硬件资源。由于FPGA具有重装载功能,可以在其内部灵活实现各种数字电路设计,甚至可以动态改变其内部设计,动态实现不同的功能。

因此,采用FPGA实现HDLC是一种可行的方法。HDLC通信控制器主要是对数据进行CRC校验、‘0’比特插入和加帧头帧尾操作。

1 “0”比特插入模块

HDLC规程规定信息的传送以帧为单位,每一帧的基本格式如图1所示。

HDLC规程指定采用8 bit的01111110为标志序列,称为F标志。用于帧同步,表示1帧的开始和结束,相邻2帧之间的F,既可作为上一帧的结束,又可作为下一帧的开始。标志序列也可以作为帧间填充字符,因而在数据链路上的各个数据站都要不断搜索F标志,以判断帧的开始和结束。

由于HDLC具有固定的帧格式,以7EH为帧头和帧尾,为了保证透明传输,即只有帧头和帧尾出现连续的6个‘l’,其他地方不允许有连续5个以上的‘l’出现,否则就要进行‘0’比特插入,即只要遇到连续5个‘1’,就在其后插入1个‘O’。根据传输数据量的大小可采用以下2种思路实现‘0’比特插入操作。

1.1 遇‘O’缓冲实现法

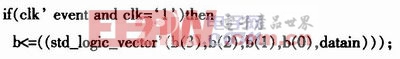

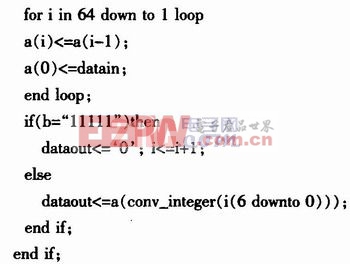

由于数据中出现多少个连续的‘1’是不可控的,故最终插入‘0’的个数也是不可控的。例如要发送的“有效数据”(包含地址字段、控制字段、信息字段、帧校验字段)为320 bit,则最多会插入64个‘0’。数据是串行输入,每插入1个‘0’,则数据由5位变成6位,则插‘0’后要输入的数据就被“积压”来,插入的‘0’越多,“积压”的数据就越多。如果采用文献中的插‘0’方法,简单的将‘O’插入,将会丢失1位数据,设置1个64位的缓冲,每插入1个‘0’就把后面数据做为1位延时,插‘0’后在把已经延时1个时钟周期的数据加进来,就保证不丢失数据。实际利用VHDL语言编译时,其VHDL代码为:

上述VHDL的思路:矢量a的第64位到第l位分别为datain延时64个时钟周期的串行数据到延时1个时钟周期的串行数据,i的初始数据为O,每遇到连续5个‘1’,插入1个‘0’后,dataout输出为datain延时i个时钟周期的数据。这样就做到了不丢失数据。图2是利用ISE 9.1i仿真的波形图。

由图2可看到插‘0’操作后,数据比未插‘0’前变长了,而且变长了多少位是由数据内容决定的。

评论